nahid99

Newbie level 4

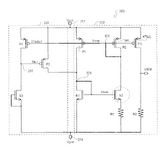

I designed a supply independent bias circuit commonly known as beta multiplier current reference. So, i used a start-up circuit to this circuit. While the transient simulation i plot the startup current, it rise up then backwards. I don't understand why it goes up to the negative side. Can anyone help me that what is the issue. Also, can anyone suggest that how to choose proper sizing for the startup circuit. Thanks