Hawaslsh

Full Member level 3

- Joined

- Mar 13, 2015

- Messages

- 171

- Helped

- 5

- Reputation

- 10

- Reaction score

- 7

- Trophy points

- 1,298

- Location

- Washington DC, USA

- Activity points

- 3,527

Hello all,

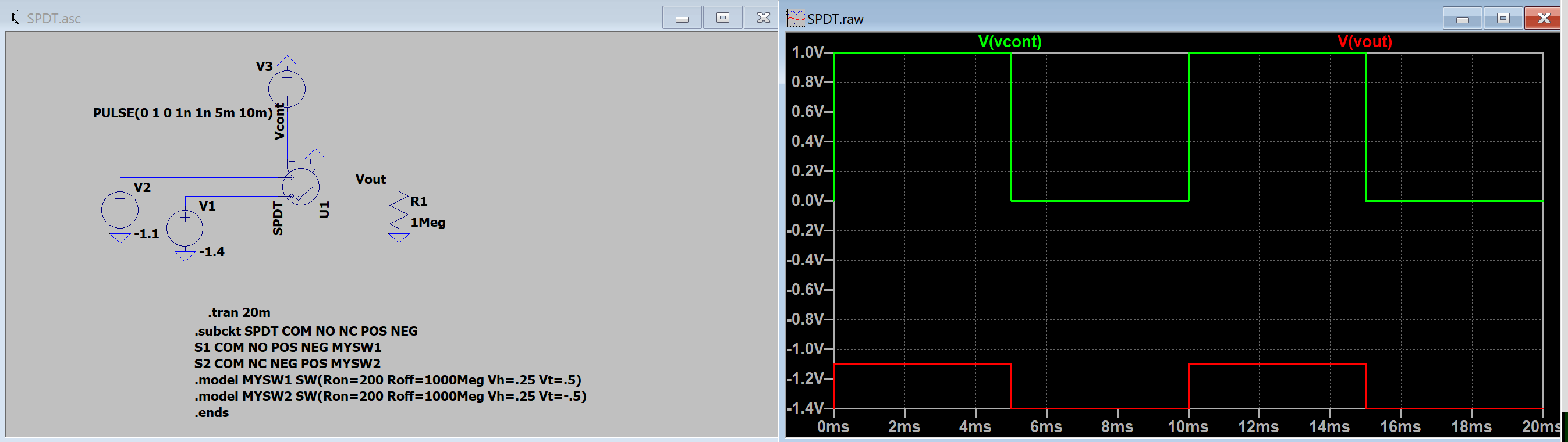

I am trying to create a SPDT switch in LT-spice. Naturally I went to google and found a decent solution, link here. I don't fully understand the how the spice directive defines the switch. Above is the recreation from the tutorial from the link which works as expected. The first line ".subckt..." defines the port names for the SPDT symbol. What/how do the next two lines "S1..." and "S2..." define the two switch states? in the third and fourth line; what is Vh and Vt?

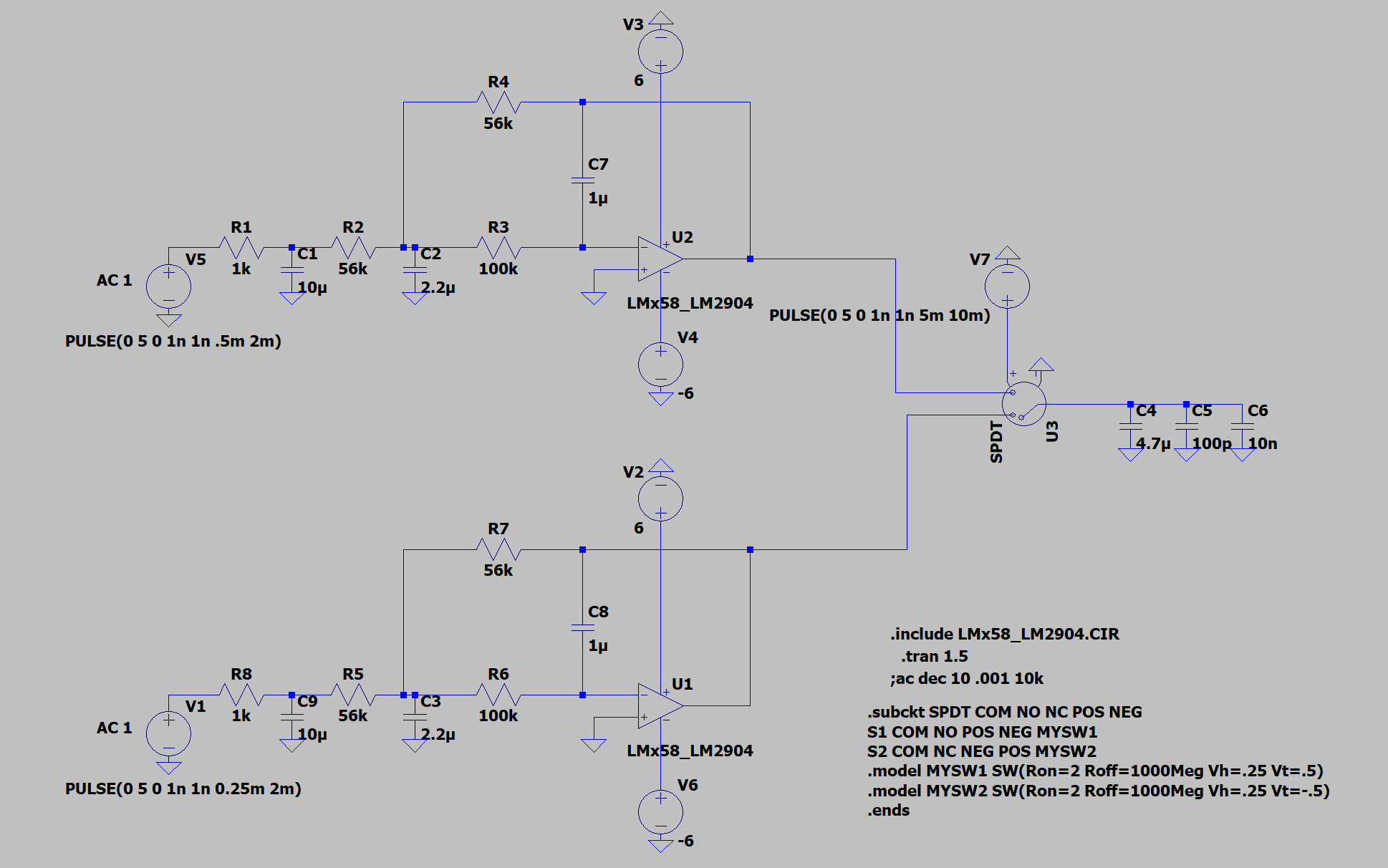

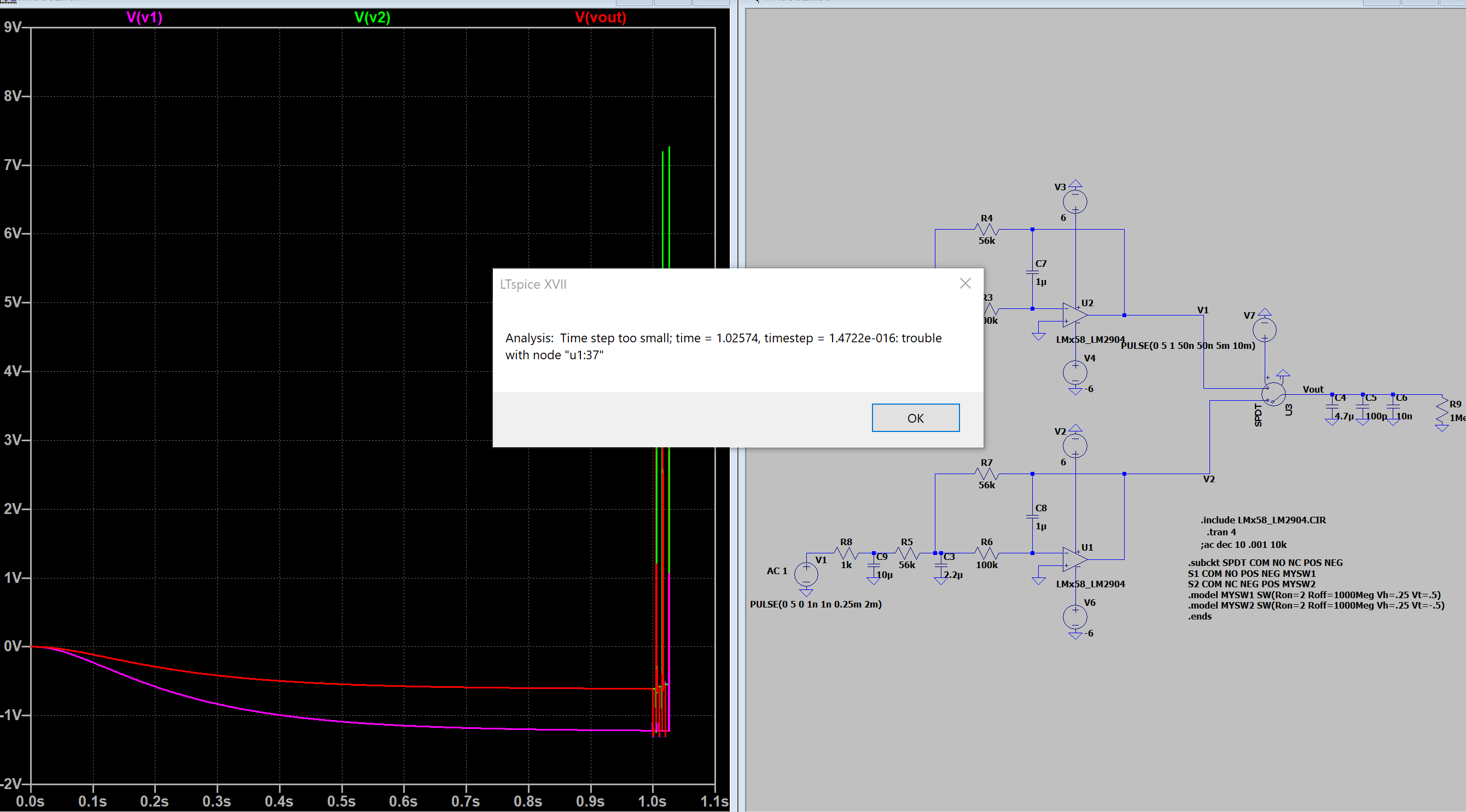

Also, I tried expanding the above example for my purposes and ran into some unexpected results. Instead of two DC supplies feeding the SPDT, I have two filtered, and inverted PWM signals, see schematic below. When I run a transient analysis to see how driving those large capacitors will look, I get a very unexpected spike shortly into the simulation.

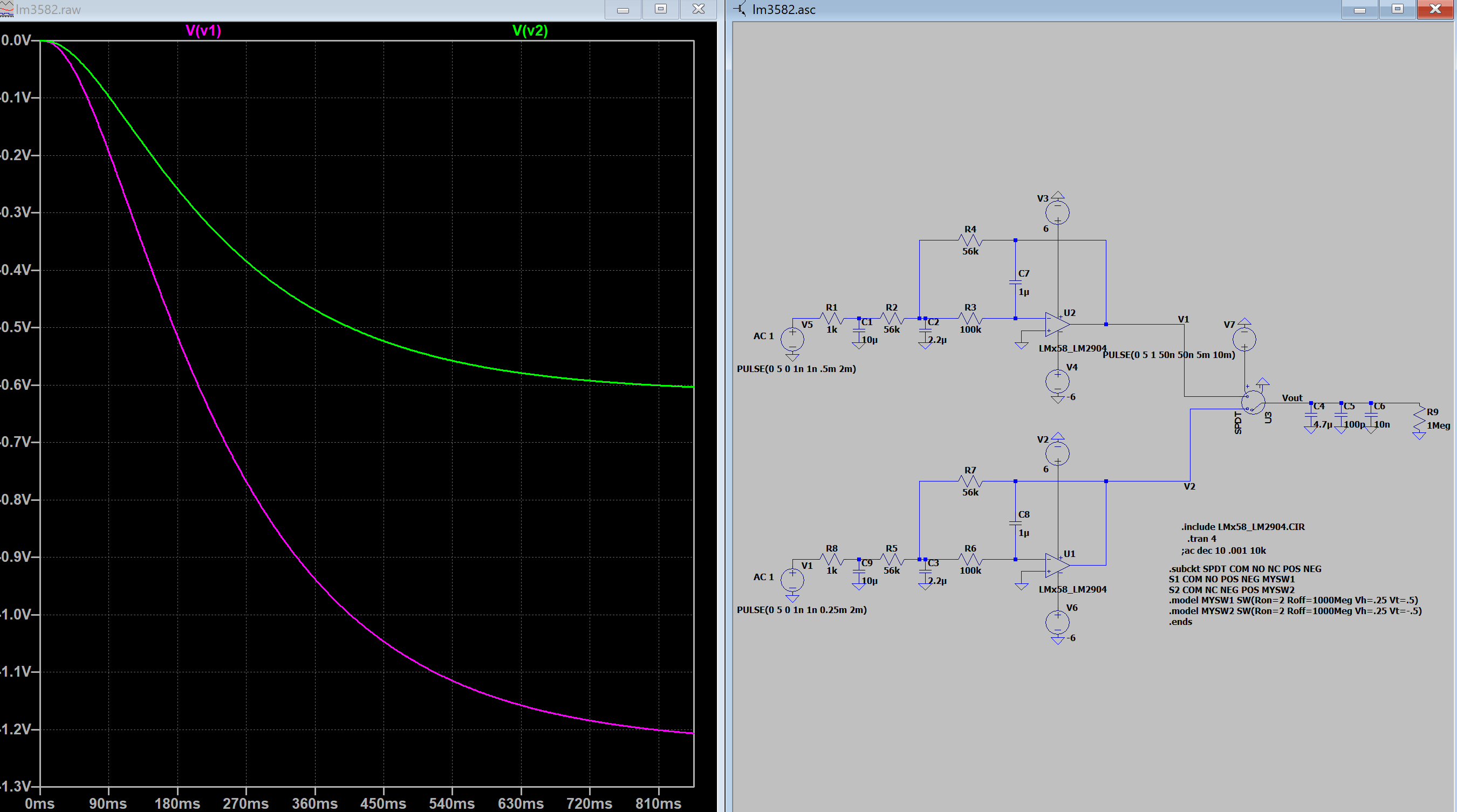

I delayed the switching for a ~1 sec (below) and plotted the inputs to the SPDT switch. With no switching the inputs to the SPDT looks as they should. The output of the SPDT lies on top of V2 and wasn't plotted to avoid confusion.

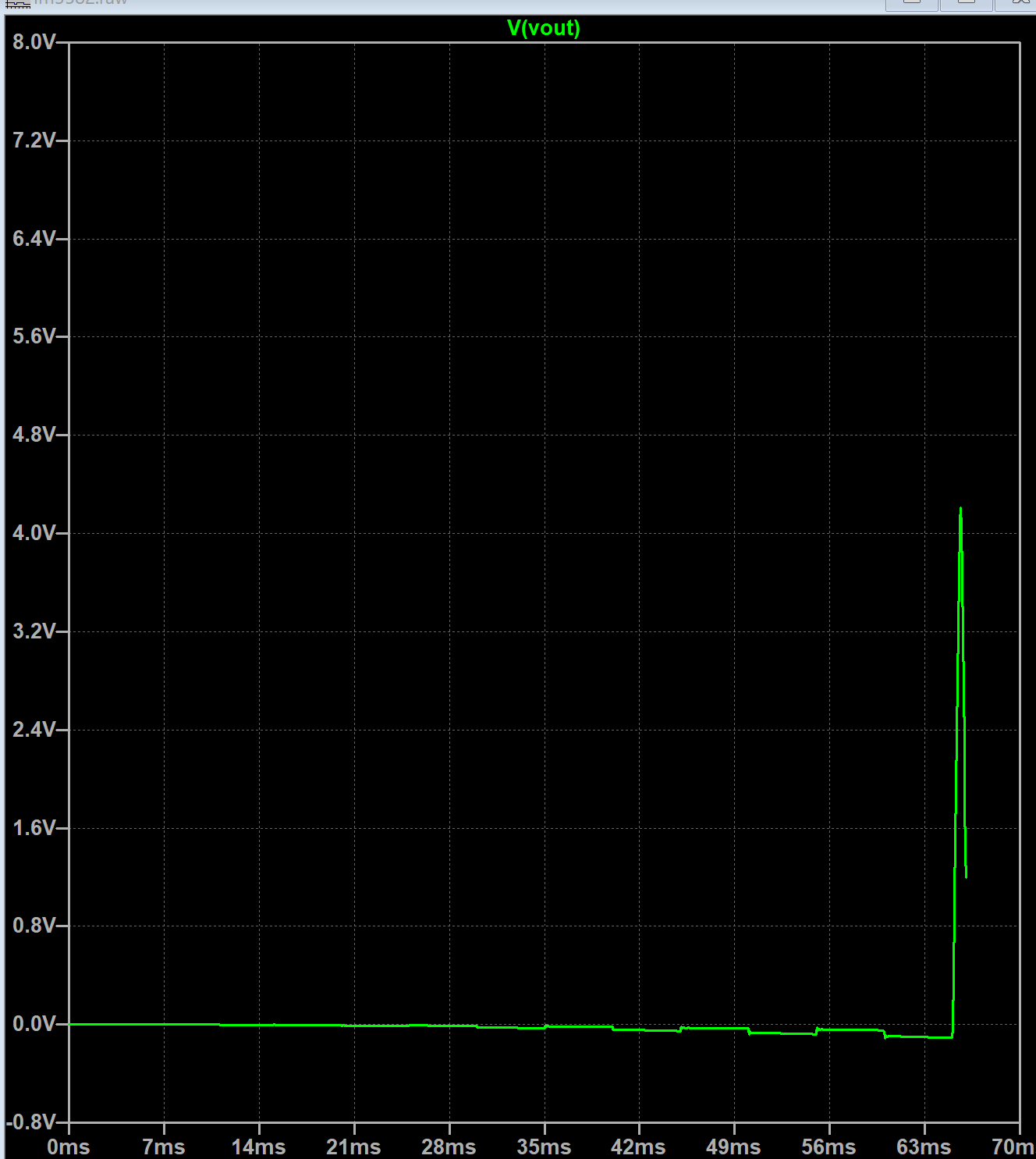

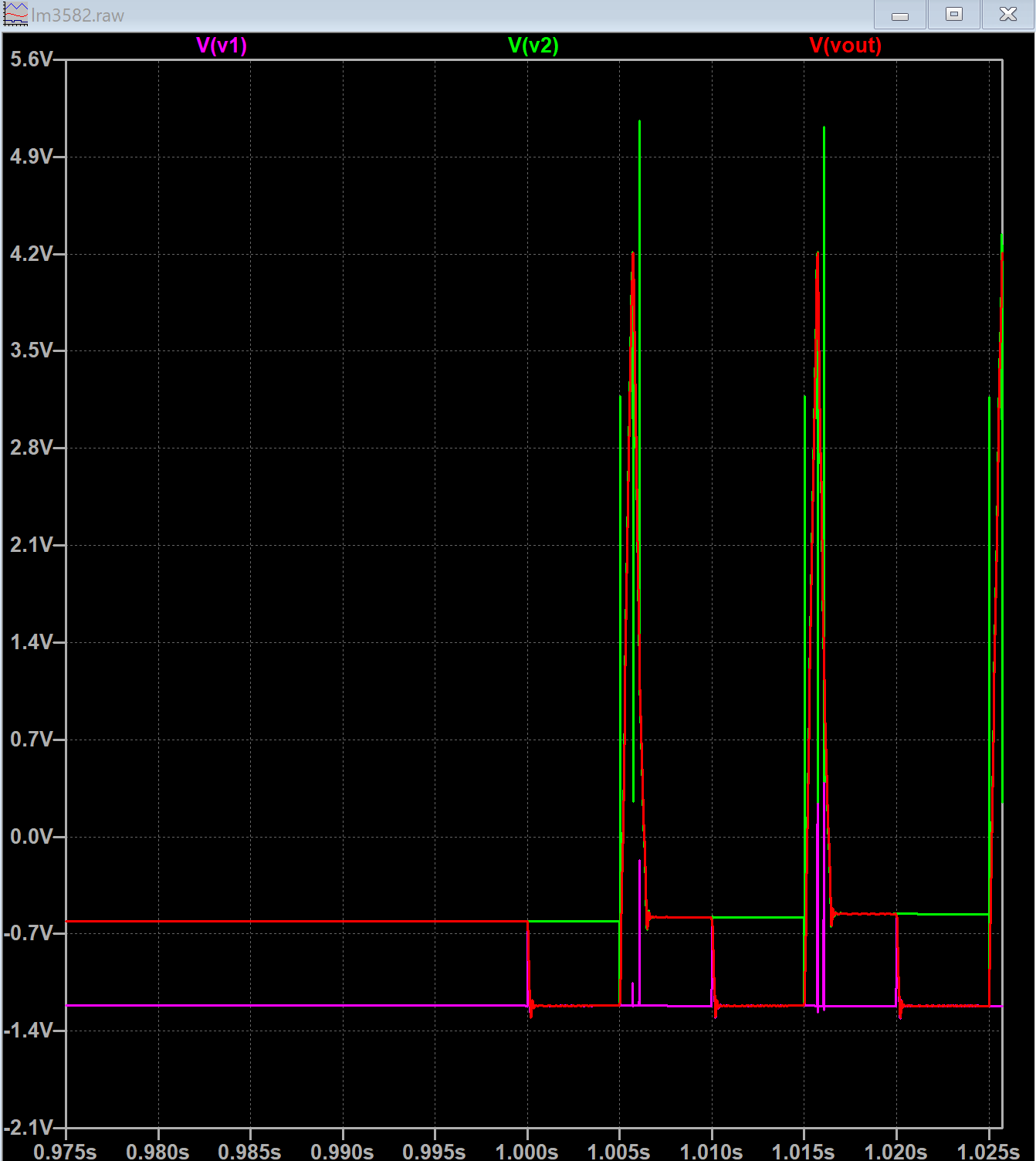

When the switching starts it seems the switch is causing serious resonance and yields in an error. The Bottom left shows the the full time and voltage scale before reaching the error. The plot on the bottom right is focused in on when the switching starts. Any idea why I am seeing these results?

Thanks in advance

Sami

I am trying to create a SPDT switch in LT-spice. Naturally I went to google and found a decent solution, link here. I don't fully understand the how the spice directive defines the switch. Above is the recreation from the tutorial from the link which works as expected. The first line ".subckt..." defines the port names for the SPDT symbol. What/how do the next two lines "S1..." and "S2..." define the two switch states? in the third and fourth line; what is Vh and Vt?

Also, I tried expanding the above example for my purposes and ran into some unexpected results. Instead of two DC supplies feeding the SPDT, I have two filtered, and inverted PWM signals, see schematic below. When I run a transient analysis to see how driving those large capacitors will look, I get a very unexpected spike shortly into the simulation.

I delayed the switching for a ~1 sec (below) and plotted the inputs to the SPDT switch. With no switching the inputs to the SPDT looks as they should. The output of the SPDT lies on top of V2 and wasn't plotted to avoid confusion.

When the switching starts it seems the switch is causing serious resonance and yields in an error. The Bottom left shows the the full time and voltage scale before reaching the error. The plot on the bottom right is focused in on when the switching starts. Any idea why I am seeing these results?

Thanks in advance

Sami