mtwieg

Advanced Member level 6

Hello, I'm in the process of debugging a LT3436 boost converter and came across the following in its datasheet:

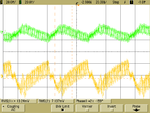

I'm concerned about this because I'm seeing bizarre instabilities in the LT3436 supply, even though I should be very well compensated and I should be operating below 50% duty cycle. It see waveforms that look like some sort of burst mode operation, though this chip isn't specified to have that capability. So I strongly suspect there's something going on inside the thing that isn't well described by the datasheet, like a variable slope compensation scheme.

Thanks in advance,

-Mike

Now, I know what subharmonic oscillation and slope compensation are, but I recall that the slope compensation is based on the downward slope of the inductor current during the off time. But here the datasheet specifies it based on the magnitude of the ripple (regardless of the input and output voltage, and thus regardless of the slopes). It does not say anything about the waveform added by their slope compensation. So I'm trying to figure out what's going on here... but I'm unable to find a resource that gives the gory details of slope compensation. I'm hoping to figure out where that 1.4App number comes from.The slope compensation circuit within the LT3436

prevents subharmonic oscillation for inductor ripple currents

of up to 1.4AP-P,

I'm concerned about this because I'm seeing bizarre instabilities in the LT3436 supply, even though I should be very well compensated and I should be operating below 50% duty cycle. It see waveforms that look like some sort of burst mode operation, though this chip isn't specified to have that capability. So I strongly suspect there's something going on inside the thing that isn't well described by the datasheet, like a variable slope compensation scheme.

Thanks in advance,

-Mike