anhnha

Full Member level 6

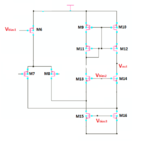

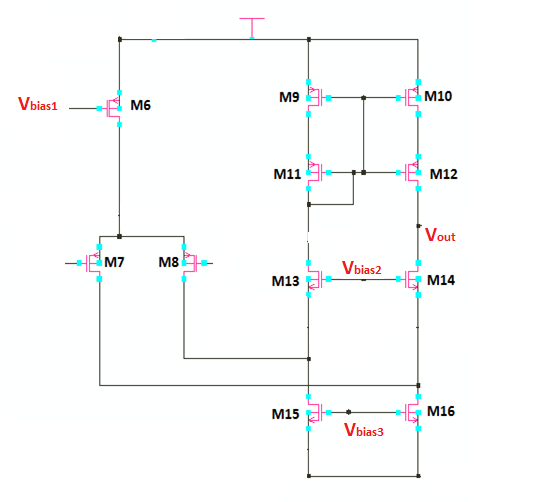

This is a folded cascode amplifier with the gain formula as follows:

Av = gm7*[gm12*rds12*rds10 || gm14*rds14*(rds16 || rds7)]

Is there a systematic way to size components so that voltage gain is as high as possible?

I am thinking about gm/Id method but how can I get load capacitance CL?

This op amp will be used for LDO but I am not sure how CL would be.

Av = gm7*[gm12*rds12*rds10 || gm14*rds14*(rds16 || rds7)]

Is there a systematic way to size components so that voltage gain is as high as possible?

I am thinking about gm/Id method but how can I get load capacitance CL?

This op amp will be used for LDO but I am not sure how CL would be.