quocviet19501

Newbie level 6

Hi everyone, thank you for reading my post.

I'm doing a project in SystemVerilog and came across this problem.

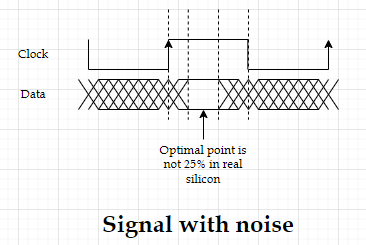

In the above figure, I want to simulate a signal that has 2 unstable edges (effect of noise in real-time environment). But I have no idea how to make the 2 edges of data unstable. I have tried some methods, but they did not work.

Can anyone suggest some ideas?

Thank you.

I'm doing a project in SystemVerilog and came across this problem.

In the above figure, I want to simulate a signal that has 2 unstable edges (effect of noise in real-time environment). But I have no idea how to make the 2 edges of data unstable. I have tried some methods, but they did not work.

Can anyone suggest some ideas?

Thank you.