promach

Advanced Member level 4

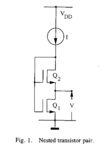

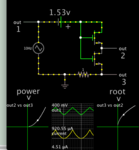

Simple CMOS Analog Square-Rooting and Squaring Circuits

For Simple CMOS Analog Square-Rooting and Squaring Circuits , how to derive equations 13 and 16 ?

For Simple CMOS Analog Square-Rooting and Squaring Circuits , how to derive equations 13 and 16 ?