ranaya

Advanced Member level 4

Hi,

I am trying come up with proper clock constraints for a mux/div clock paths.

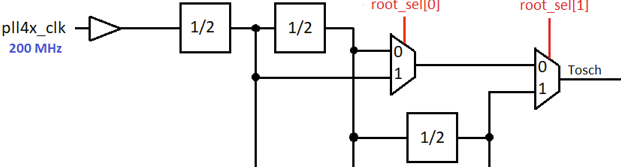

The design structure looks like below:

pll4x_clk is an input to the block, so that the output Tosch of the block has pll4x_clk/2, 4 and 8 options.

How to properly write the constraints in a way clocks are nicely converged ?

From this point onwards how to specify the multiplexed paths for Tosch ?

Thanks in advance.

I am trying come up with proper clock constraints for a mux/div clock paths.

The design structure looks like below:

pll4x_clk is an input to the block, so that the output Tosch of the block has pll4x_clk/2, 4 and 8 options.

How to properly write the constraints in a way clocks are nicely converged ?

Code:

create_clock -name pll_out4x_clk -period 5.00 [get_ports pll_out4x_clk]

#pll4x divided by 2, 4, 8

create_generated_clock -name clk_div2 -divide_by 2 -source pll_out4x_clk [get_pins fast_div2/clk_div2]

create_generated_clock -name clk_div4 -divide_by 2 -source [get_pins fast_div2/clk_div2] [get_pins fast_div4/clk_div2]

create_generated_clock -name clk_div8 -divide_by 2 -source [get_pins fast_div4/clk_div2] [get_pins fast_div8/clk_div2]

set_clock_groups -logically_exclusive -group clk_div2 -group clk_div4 -group clk_div8From this point onwards how to specify the multiplexed paths for Tosch ?

Thanks in advance.

Last edited by a moderator: