yefj

Advanced Member level 5

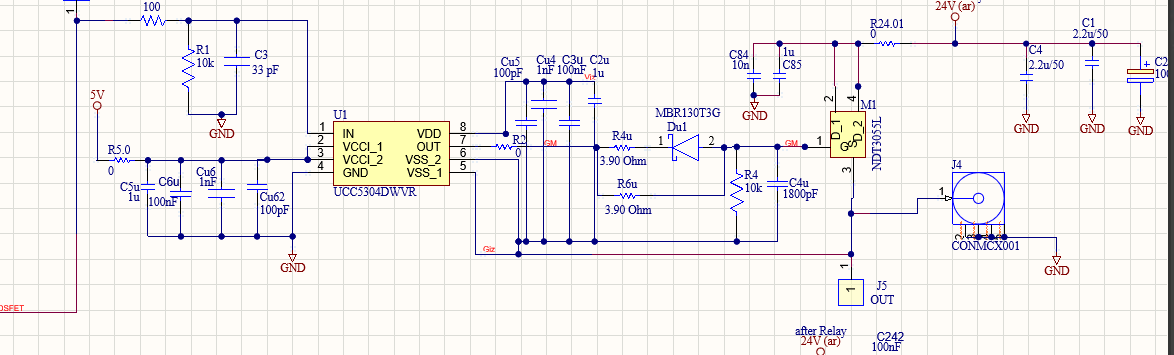

Hello,In the diagram sown below I have a MOSFET called NDT3055L, the mosfet sends the current into the Qorvo TGA2590-CP drain.

When we test the circuit the source of the mosfet is basically floating although when I will connect the amplifier to source then the QORVO amplifier will introduce a load to the source of the mosfet.

Somehow the optocoupler helps with the transition of the state when we don't have QORVO amplifier load on the source of the MOSFET.

What is the role of the optocoupler in this situation?

I'll be glad to have some analog design logic behind putting this component in this position.

Thanks.

www.qorvo.com

www.qorvo.com

When we test the circuit the source of the mosfet is basically floating although when I will connect the amplifier to source then the QORVO amplifier will introduce a load to the source of the mosfet.

Somehow the optocoupler helps with the transition of the state when we don't have QORVO amplifier load on the source of the MOSFET.

What is the role of the optocoupler in this situation?

I'll be glad to have some analog design logic behind putting this component in this position.

Thanks.