Junus2012

Advanced Member level 5

Hello,

In the technology I am working I have the common corners for the MOSFET :

FF, SS, FS, SF

Those corners are clear from me, like FF means fast NMOS and fast PMOS, SS means slow NMOS and slow PMOS, FS means fast NMOS and slow PMOS and SF mean slow NMOS and fast PMOS.

The fast and slow terms I can connect it to the gate oxide thickness and then to threshold voltage variation,

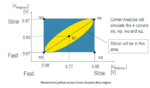

The thing which I don't understand, how in the process the NMOS can be slow and PMOS fast (SF) or the reverse at FS ?

The second important thing for me which I didnt understand yet, for my resistor and capacitor model technology I have only FF and SS, beside for sur the typical mean TT, and I dont know what FF or SS means for capacitor and resistor, I am expecting the FF will make both capacitor and resistor smaller while SS makes them bigger.

My main problem is just right now coming

In the corner simulation, I setting up the process corners for my circuit,

you see that for MOSFET they have four corners beside TT, while for resistor and capacitor they have only two,

A possible solution that I cover all possible corners just like a digital inputs, means that I can have a corner setting like this

MOSFET FF, resistor FF, capacitor FF

MOSFET SS, resistor SS, capacitor SS

For the above table I have no issue. my issue for example like below setting

MOSFET FF, resistor SS, capacitor FF

MOSFET SS, resistor FF, capacitor SS

......

.

.

.

.

............ etc,

mean is it possible to have different condition for every component from other component ? by simulation there is no problem and he accept any combination, but is that realistic combination, I am thinking that such kind of combination might never exists in real fabrication ?

Thank you very much in advance

Best regards

In the technology I am working I have the common corners for the MOSFET :

FF, SS, FS, SF

Those corners are clear from me, like FF means fast NMOS and fast PMOS, SS means slow NMOS and slow PMOS, FS means fast NMOS and slow PMOS and SF mean slow NMOS and fast PMOS.

The fast and slow terms I can connect it to the gate oxide thickness and then to threshold voltage variation,

The thing which I don't understand, how in the process the NMOS can be slow and PMOS fast (SF) or the reverse at FS ?

The second important thing for me which I didnt understand yet, for my resistor and capacitor model technology I have only FF and SS, beside for sur the typical mean TT, and I dont know what FF or SS means for capacitor and resistor, I am expecting the FF will make both capacitor and resistor smaller while SS makes them bigger.

My main problem is just right now coming

In the corner simulation, I setting up the process corners for my circuit,

you see that for MOSFET they have four corners beside TT, while for resistor and capacitor they have only two,

A possible solution that I cover all possible corners just like a digital inputs, means that I can have a corner setting like this

MOSFET FF, resistor FF, capacitor FF

MOSFET SS, resistor SS, capacitor SS

For the above table I have no issue. my issue for example like below setting

MOSFET FF, resistor SS, capacitor FF

MOSFET SS, resistor FF, capacitor SS

......

.

.

.

.

............ etc,

mean is it possible to have different condition for every component from other component ? by simulation there is no problem and he accept any combination, but is that realistic combination, I am thinking that such kind of combination might never exists in real fabrication ?

Thank you very much in advance

Best regards