antlhem

Member level 1

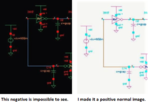

I am making tests with a ring oscillator (RO) in ADEL Cadence. But when I increase the size of the RO from 13 to 121 stages there are glitches in the output signal of the RO (image attached). How can I make the output frequency of the RO a stable signal? Because this is also generating errors for aging simulation in ADEL.