Maitry07

Full Member level 2

Hello support team,

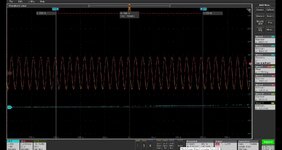

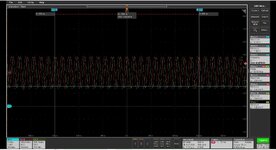

I am working on a high speed ADC + FPGA . High speed ADC is multi channel that can take CW tone RF input and convert it into decimated I,Q digital data through DDC technique. I am providing 40 MHz RF input to high speed ADC channel 1 and channel 2 with the same cable length through function generator. My FG's channel 1 phase is 9.058 deg while My FG's channel 2 phase is 0 deg. FYI: I have checked my input's phase difference in MSO and validate that it is 9.058 deg

My FPGA is capturing decimated digital I,Q data for both the channels simultanously and I am using CORDIC IP core to convert the I,Q to absolute phase for both channel 1 and channel 2.

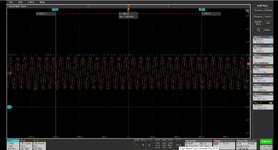

now, I am using subtractor IP core to have a difference between absolute phase 1- absolute phase 2 to generate relative phase.

and when I am checking output of relative phase , it is approximately 15 deg instead of 9.058 deg. weather this variation is due to slight mismatch between both the front end channel of my high speed ADC?

FYI: I am using AFE7900 High speed ADC.

What need to be done in order to compensate this relative phase misatch? is it ok to subtract 6 deg from the final relative phase output or any other proven method you can suggest to compensate this relative phase mismatch?

Awaited your response. if you need any other details, do let me know.

I am working on a high speed ADC + FPGA . High speed ADC is multi channel that can take CW tone RF input and convert it into decimated I,Q digital data through DDC technique. I am providing 40 MHz RF input to high speed ADC channel 1 and channel 2 with the same cable length through function generator. My FG's channel 1 phase is 9.058 deg while My FG's channel 2 phase is 0 deg. FYI: I have checked my input's phase difference in MSO and validate that it is 9.058 deg

My FPGA is capturing decimated digital I,Q data for both the channels simultanously and I am using CORDIC IP core to convert the I,Q to absolute phase for both channel 1 and channel 2.

now, I am using subtractor IP core to have a difference between absolute phase 1- absolute phase 2 to generate relative phase.

and when I am checking output of relative phase , it is approximately 15 deg instead of 9.058 deg. weather this variation is due to slight mismatch between both the front end channel of my high speed ADC?

FYI: I am using AFE7900 High speed ADC.

What need to be done in order to compensate this relative phase misatch? is it ok to subtract 6 deg from the final relative phase output or any other proven method you can suggest to compensate this relative phase mismatch?

Awaited your response. if you need any other details, do let me know.