Joaquin Piñeiro

Newbie

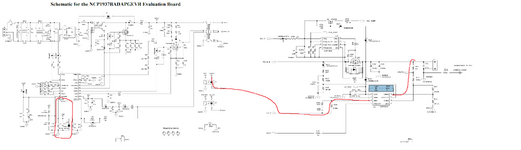

Hi! I'm doing a SMPS of 120W using a reference design from onsemi NCP1937BADAPGEVB.

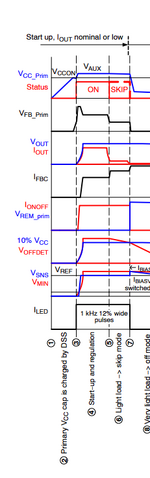

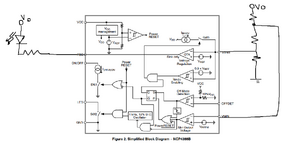

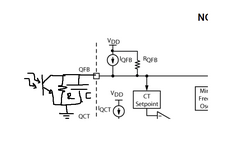

I did a lot of reverse engeneering in this design due to lack of information provided in the datasheet of NCP1937, although it has 40 pages. To achive regulation, NCP4355 (U4) is the solution provided by de reference design. In the regulation path, an optocoupler (U2) is connected to FBB pin in NCP4355, which drives a current that comes from an OTA. This OTA is controlled by a diferential voltage, which is a reference voltage and the output voltage scaled.

So if the voltage goes up, a current will start increasing at the diode of U2, and therefore the IC of phototransistor too. This current is very important because, sets the voltage at QFB pin in NCP1937 by R24, and with the internal components (IQFB, RQFB, VDD). The problem is that voltage at this pin could swing between 4.1V and 0.4V when is Vo at nominal load and Vo at minimum load, and that excursion is a delta current in the phototransistor in the order of micro amps. This means that current sinking from the OTA is in the order of micro amps too, giving a delta Vo in the order of micro volts. Datasheet of NCP4355 specifies that minimum current at OTA in regultion is at least 2mA. So how is this possible?

Thanks in advance.

I did a lot of reverse engeneering in this design due to lack of information provided in the datasheet of NCP1937, although it has 40 pages. To achive regulation, NCP4355 (U4) is the solution provided by de reference design. In the regulation path, an optocoupler (U2) is connected to FBB pin in NCP4355, which drives a current that comes from an OTA. This OTA is controlled by a diferential voltage, which is a reference voltage and the output voltage scaled.

So if the voltage goes up, a current will start increasing at the diode of U2, and therefore the IC of phototransistor too. This current is very important because, sets the voltage at QFB pin in NCP1937 by R24, and with the internal components (IQFB, RQFB, VDD). The problem is that voltage at this pin could swing between 4.1V and 0.4V when is Vo at nominal load and Vo at minimum load, and that excursion is a delta current in the phototransistor in the order of micro amps. This means that current sinking from the OTA is in the order of micro amps too, giving a delta Vo in the order of micro volts. Datasheet of NCP4355 specifies that minimum current at OTA in regultion is at least 2mA. So how is this possible?

Thanks in advance.