Reducing switching noise in MOSFET inverter

- Thread starter mike buba

- Start date

- Status

- Not open for further replies.

Solution

Hi,

The most important is a schematic: Where is the source of noise, where to put the filter, which filter.

But almost equally important is the PCB layout. The fancy filter is useless if the PCB layout is bad. A bad PCB layout can make a filter almost useless.

Klaus

The most important is a schematic: Where is the source of noise, where to put the filter, which filter.

But almost equally important is the PCB layout. The fancy filter is useless if the PCB layout is bad. A bad PCB layout can make a filter almost useless.

Klaus

KlausST

Advanced Member level 7

Hi,

The most important is a schematic: Where is the source of noise, where to put the filter, which filter.

But almost equally important is the PCB layout. The fancy filter is useless if the PCB layout is bad. A bad PCB layout can make a filter almost useless.

Klaus

The most important is a schematic: Where is the source of noise, where to put the filter, which filter.

But almost equally important is the PCB layout. The fancy filter is useless if the PCB layout is bad. A bad PCB layout can make a filter almost useless.

Klaus

mtwieg

Advanced Member level 6

I've used a few different debug tools for C2000 MCUs, including the ones integrated into the controlcards and plug-in debug probes on custom boards. Just try different setups and observe what happens. In my case the results were often surprising and didn't require modifying the power circuitry itself.

1. USB cables. Some cables just had more issues than others, perhaps due to differences in shielding or due to having different ferrite beads integrated in the cable. Try adding ferrite(s) to the cable yourself.

2. Isolation. I'm betting you're using a controlcard with an xds100, and it has isolation of the JTAG signals. Normally isolation does help a lot, but in some cases I had better luck by shorting out the isolation barrier (especially if my clk frequency was high).

3. Your PC. I often saw less problems when using a laptop which was unconnected to any other peripherals (including its power adaptor). Not always practical of course. You should be able to get the same effect with good cabling.

4. Earth connections. This is highly dependent on your circuit, but I've observed that connections from the power circuitry to earth can matter significantly. This includes the gnd clips of oscilloscopes probing the power circuitry.

5. The debug tool. My preferred option is an xds200 with a JTAG isolation adaptor (ISO14 from Blackhawk). Main reason I use it is because the xds200 is significantly faster than the xds100. However I don't see why this would perform any worse than the isolated debug probe on the controlcard already. But others, including myself, have reported that it helps with issues like yours. It is pretty expensive though...

Anyways I would spend time trying different USB cables and ferrites before touching the power circuitry.

Also you should check that the issue isn't conducted noise to the target MCU. Check its supply rails for dips and spikes, and also the reset pin for false triggers. Such issues can produce behavior which imitates a failure of the debug tool.

1. USB cables. Some cables just had more issues than others, perhaps due to differences in shielding or due to having different ferrite beads integrated in the cable. Try adding ferrite(s) to the cable yourself.

2. Isolation. I'm betting you're using a controlcard with an xds100, and it has isolation of the JTAG signals. Normally isolation does help a lot, but in some cases I had better luck by shorting out the isolation barrier (especially if my clk frequency was high).

3. Your PC. I often saw less problems when using a laptop which was unconnected to any other peripherals (including its power adaptor). Not always practical of course. You should be able to get the same effect with good cabling.

4. Earth connections. This is highly dependent on your circuit, but I've observed that connections from the power circuitry to earth can matter significantly. This includes the gnd clips of oscilloscopes probing the power circuitry.

5. The debug tool. My preferred option is an xds200 with a JTAG isolation adaptor (ISO14 from Blackhawk). Main reason I use it is because the xds200 is significantly faster than the xds100. However I don't see why this would perform any worse than the isolated debug probe on the controlcard already. But others, including myself, have reported that it helps with issues like yours. It is pretty expensive though...

Anyways I would spend time trying different USB cables and ferrites before touching the power circuitry.

Also you should check that the issue isn't conducted noise to the target MCU. Check its supply rails for dips and spikes, and also the reset pin for false triggers. Such issues can produce behavior which imitates a failure of the debug tool.

Last edited:

mike buba

Member level 3

Hi Klaus, thank you for the reply.Hi,

The most important is a schematic: Where is the source of noise, where to put the filter, which filter.

But almost equally important is the PCB layout. The fancy filter is useless if the PCB layout is bad. A bad PCB layout can make a filter almost useless.

Klaus

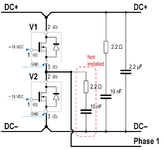

I have contracted a PCB design and manufacturing based on my top-level electrical circuit design. I am not that skilled in PCB design and debugging. Snubber elements from the schematics are highlighted in the top and bottom assembly view.

Commissioning a new PCB design would not be on top of the list... especially since I don't know why the noise is happening in the first place.

--- Updated ---

Hi mtwieg, thank you for the reply.

I am already using a USB isolator between ControlCard and PC (laptop) (this one), supplied via an isolation transformer1. USB cables. Some cables just had more issues than others, perhaps due to differences in shielding or due to having different ferrite beads integrated in the cable. Try adding ferrite(s) to the cable yourself.

Yes. xds100. I was advised to remove ground cap A:C31 on the controlCard (link to TI forum thread). Not sure if you are referring to this isolation.2. Isolation. I'm betting you're using a controlcard with an xds100, and it has isolation of the JTAG signals. Normally isolation does help a lot, but in some cases I had better luck by shorting out the isolation barrier (especially if my clk frequency was high).

Removing the cap helped. But still, the noise was there at higher voltages and powers and communication kept breaking. Then I reduced the gate resistance by 1/3. This also reduced the noise slightly. At the moment I am at 600 Vdc and I need to get to 650-670 Vdc for 3x400 Vac output. Before removing capacitor A:C3, the max. DC voltage before comms breaking was 200 Vdc.

My laptop is powerd from another isolation transformer. No change even if it's powered from the battery.3. Your PC. I often saw less problems when using a laptop which was unconnected to any other peripherals (including its power adaptor). Not always practical of course. You should be able to get the same effect with good cabling.

The oscilloscope is also powered via an isolation transformer. Cubicle is grounded.4. Earth connections. This is highly dependent on your circuit, but I've observed that connections from the power circuitry to earth can matter significantly. This includes the gnd clips of oscilloscopes probing the power circuitry.

This was the last suggestion from TI. To get a more robust external isolated emulator, e.g. Blackhawk.5. The debug tool. My preferred option is an xds200 with a JTAG isolation adaptor (ISO14 from Blackhawk). Main reason I use it is because the xds200 is significantly faster than the xds100. However I don't see why this would perform any worse than the isolated debug probe on the controlcard already. But others, including myself, have reported that it helps with issues like yours. It is pretty expensive though...

I have external ferrites put on the input power supply cable, +/-15 Vdc board supply cable, and output load cable. Most of the cables are shielded. But even ferrites "work" only above 100 kHz.Anyways I would spend time trying different USB cables and ferrites before touching the power circuitry.

Also you should check that the issue isn't conducted noise to the target MCU. Check its supply rails for dips and spikes, and also the reset pin for false triggers. Such issues can produce behavior which imitates a failure of the debug tool.

Last edited:

mtwieg

Advanced Member level 6

Ok looks like you've already tried a lot of the basic things

Can you show a photo of your setup? Those pics of the board layout don't include where the controlcard is, I assume. I assume those boxes on the top layer (x100, x101, etc) are daughterboards with gate drivers on them? And I guess the 6 pin connectors to the left connect to the controlcard somewhere else?

Ok, but that's at best redundant with the existing isolation on the xds100I am already using a USB isolator between ControlCard and PC (laptop) (this one), supplied via an isolation transformer

Yes, not surprising that removing it had a large effect, I think I observed the same thing long ago. There were also rare cases where shorting this isolation barrier helped but that's much more risky and I wouldn't expect it to help in most cases.Yes. xds100. I was advised to remove ground cap A:C31 on the controlCard (link to TI forum thread). Not sure if you are referring to this isolation.

Removing the cap helped. But still, the noise was there at higher voltages and powers and communication kept breaking. Then I reduced the gate resistance by 1/3. This also reduced the noise slightly. At the moment I am at 600 Vdc and I need to get to 650-670 Vdc for 3x400 Vac output. Before removing capacitor A:C3, the max. DC voltage before comms breaking was 200 Vdc.

These isolation transformers could have enough capacitance across the isolation barrier to make the isolation ineffective at very high frequencies. For example, that A:C31 was only 1nF and that made a big difference, and isolation transformers can easily have that much.My laptop is powerd from another isolation transformer. No change even if it's powered from the battery.

The oscilloscope is also powered via an isolation transformer. Cubicle is grounded.

I have external ferrites put on the input power supply cable, +/-15 Vdc board supply cable, and output load cable. Most of the cables are shielded. But even ferrites "work" only above 100 kHz.

Can you show a photo of your setup? Those pics of the board layout don't include where the controlcard is, I assume. I assume those boxes on the top layer (x100, x101, etc) are daughterboards with gate drivers on them? And I guess the 6 pin connectors to the left connect to the controlcard somewhere else?

mike buba

Member level 3

Bottom: Inverter card (PCB layout shown in one of the previous posts). X100, X101, ... X400, X401 are places for MOSFET drivers. Eight connectors on the side are for PWM pulses. On the bottom side are mounted MOSFETS on a heatsink (not grounded). A lower leg RC snubber components are not mounted.Can you show a photo of your setup? Those pics of the board layout don't include where the controlcard is, I assume. I assume those boxes on the top layer (x100, x101, etc) are daughterboards with gate drivers on them? And I guess the 6 pin connectors to the left connect to the controlcard somewhere else?

Middle level: Measurement card for measuring voltages and currents and capacitors for LC filter.

Top level: Signal conditioning card and ControlCard. On the right side are analogue inputs and on the left side are PWM inputs. Bottom left connector for +/-15 Vdc and 0 Vdc. I put this card in a separate grounded metallic enclosure.

This is all in a cubicle together with other components: DC/DC converter (IGBT, inductor, capacitors) and LC filter's inductors, +/-15 Vdc supply.

mtwieg

Advanced Member level 6

Ah ok your gate drivers are also isolated as well. With multiple isolation barriers, and lots of physical separation between the inverter and control card, I'm actually surprised you're having these issues at all.

In fact, having so many isolation barriers might be part of the issue. I'm guessing the AC supply for your PFC stage is isolated as well. Is the GND net of the inverter/boost converter connected to earth/chassis, either directly or through a Y capacitor? If not, then that whole circuit may have tons of high frequency common mode voltage on it, which could easily cause your problems (try probing it with your scope, with the probe's ground clip not connected to anything). I'd at least add a proper Y-rated capacitor (2.2nF is probably a safe starting point), if not a direct short (so long as your source/load is isolated) to earth. Make sure that path to earth is not shared with any sensitive circuitry.

In fact, having so many isolation barriers might be part of the issue. I'm guessing the AC supply for your PFC stage is isolated as well. Is the GND net of the inverter/boost converter connected to earth/chassis, either directly or through a Y capacitor? If not, then that whole circuit may have tons of high frequency common mode voltage on it, which could easily cause your problems (try probing it with your scope, with the probe's ground clip not connected to anything). I'd at least add a proper Y-rated capacitor (2.2nF is probably a safe starting point), if not a direct short (so long as your source/load is isolated) to earth. Make sure that path to earth is not shared with any sensitive circuitry.

Easy peasy

Advanced Member level 6

OK - you have the classic newbie problem - dv/dt noise getting into everything as the bus volts go up

You talk about " reducing " the gate resistors above - when in the context of your sentences I assume you mean increasing instead. This does depend on the frequency of operation - at 4kHz (?) you are pretty safe.

what are the gate resistors you have tried ? with what results ?

snubbers with very short leads across every switching semi is a good start, say 1nF ( 2kV rated ) and 220 ohms low inductance resistors - at 4kHz these R's will dissipate 1.8W, so 2 x 470 ohm in parallel ( 3W ea ) with their leads ( one end ) soldered direct to the drain of the devices to provide a little heatsinking, will stop the smoke coming out of the snubber resistors/capacitors.

Next is the heatsink, if it is earthed you are in trouble - worse still if left floating - as that is how the RF noise is propagating - so either connect the heatsink to the local 0v of the HVDC bus ( no earth ) or put a 0V shield under the devices who have the tabs at switching freq ( all the lower devices ) so a 3 layer sandwhich - Tab - ins - shield - ins - earthed heatsink. The shield must have a short connection to the local 0v.

Now the gate resistors, set the Rg = 100 ohms, with a back diode ( 40V 1A schottky ) and 10 ohm resistor in series with the diode across the 100 ohm to give fast turn off. Diode cathode points to driver.

Then report back to the group.

Oh - and also - solder a good quality film/foil cap directly across each totem pole pair, say anyrhing from 470n to 4u7 and 800V - this will help with overshoot on the devices at turn off - which you presumably haven't even looked at yet. Then also help limit di/dt induced noise from radiating off the board ...

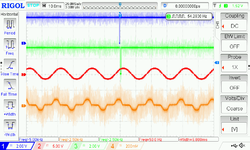

Don't forget to show real switching waveforms in the next post.

p.p.s

your waveforms look more like 40kHz in the above - even though you wrote 4kHz

for 40kHz the shubber caps should be 220 - 270pF max for 670VDC bus - else the resistors will catch fire.

You talk about " reducing " the gate resistors above - when in the context of your sentences I assume you mean increasing instead. This does depend on the frequency of operation - at 4kHz (?) you are pretty safe.

what are the gate resistors you have tried ? with what results ?

snubbers with very short leads across every switching semi is a good start, say 1nF ( 2kV rated ) and 220 ohms low inductance resistors - at 4kHz these R's will dissipate 1.8W, so 2 x 470 ohm in parallel ( 3W ea ) with their leads ( one end ) soldered direct to the drain of the devices to provide a little heatsinking, will stop the smoke coming out of the snubber resistors/capacitors.

Next is the heatsink, if it is earthed you are in trouble - worse still if left floating - as that is how the RF noise is propagating - so either connect the heatsink to the local 0v of the HVDC bus ( no earth ) or put a 0V shield under the devices who have the tabs at switching freq ( all the lower devices ) so a 3 layer sandwhich - Tab - ins - shield - ins - earthed heatsink. The shield must have a short connection to the local 0v.

Now the gate resistors, set the Rg = 100 ohms, with a back diode ( 40V 1A schottky ) and 10 ohm resistor in series with the diode across the 100 ohm to give fast turn off. Diode cathode points to driver.

Then report back to the group.

--- Updated ---

Oh - and also - solder a good quality film/foil cap directly across each totem pole pair, say anyrhing from 470n to 4u7 and 800V - this will help with overshoot on the devices at turn off - which you presumably haven't even looked at yet. Then also help limit di/dt induced noise from radiating off the board ...

Don't forget to show real switching waveforms in the next post.

--- Updated ---

p.p.s

your waveforms look more like 40kHz in the above - even though you wrote 4kHz

for 40kHz the shubber caps should be 220 - 270pF max for 670VDC bus - else the resistors will catch fire.

Last edited:

mtwieg

Advanced Member level 6

Agreed with all above. The comments about electrical connection to the heatsink deserves some more detail:

From an EMC standpoint, the ideal connection for the heatsink would be directly to the power circuitry's reference plane (either side of the DC bus), since that's where RFI "wants" to return to. But usually the heatsink must be at chassis/protective earth GND for mechanical/thermal reasons. If your source/load are isolated, you can try connecting the two together.

Connecting the heatsink to chassis GND is usually better than letting it float, though. Providing a EMI filter where the AC mains enters the chassis is then key for controlling RFI. The Y caps in the filter should provide a decent return path for the RFI, so it stays mostly within the chassis.

One trick I've seen mentioned in literature is to have your heatsink at chassis GND, but put a thin metal screen in between the semiconductors and the heatsink, with TIM on both sides. The screen is connected to the power circuitry reference plane, which greatly reduces the RFI which makes it to chassis GND. Never seen this in practice though.

And yes, it's worth fitting those RF snubbers on all the bridges. Just make sure the resistors can tolerate the dissipation. The footprints on the layout you showed look insufficient, but I suppose there's no reason you can't hack on a bigger package at this stage.

From an EMC standpoint, the ideal connection for the heatsink would be directly to the power circuitry's reference plane (either side of the DC bus), since that's where RFI "wants" to return to. But usually the heatsink must be at chassis/protective earth GND for mechanical/thermal reasons. If your source/load are isolated, you can try connecting the two together.

Connecting the heatsink to chassis GND is usually better than letting it float, though. Providing a EMI filter where the AC mains enters the chassis is then key for controlling RFI. The Y caps in the filter should provide a decent return path for the RFI, so it stays mostly within the chassis.

One trick I've seen mentioned in literature is to have your heatsink at chassis GND, but put a thin metal screen in between the semiconductors and the heatsink, with TIM on both sides. The screen is connected to the power circuitry reference plane, which greatly reduces the RFI which makes it to chassis GND. Never seen this in practice though.

And yes, it's worth fitting those RF snubbers on all the bridges. Just make sure the resistors can tolerate the dissipation. The footprints on the layout you showed look insufficient, but I suppose there's no reason you can't hack on a bigger package at this stage.

mike buba

Member level 3

Quick update.

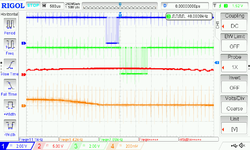

I can go now up to 650 Vdc and full power without serial communication breaking down

First, I increased gare resistance from 6.66 Ohm to 10 Ohm (max. DC voltage before comms breaking was 600 Vdc). Now I have it at 23.5 Ohm (Rgon and Rgoff) and I can go up to 650 Vdc.

In the next step, I added a Ceramic Capacitors (0.01 µF, 2 kV) across lower IGBTs in each inverter leg. This also reduced the noise. I think this looks good and shouldn't be any problems going forward. Ideally, I would like to add capacitors across upper IGBTs; not sure if this is needed and there are no PCB pads for that on the board.

I can go now up to 650 Vdc and full power without serial communication breaking down

First, I increased gare resistance from 6.66 Ohm to 10 Ohm (max. DC voltage before comms breaking was 600 Vdc). Now I have it at 23.5 Ohm (Rgon and Rgoff) and I can go up to 650 Vdc.

In the next step, I added a Ceramic Capacitors (0.01 µF, 2 kV) across lower IGBTs in each inverter leg. This also reduced the noise. I think this looks good and shouldn't be any problems going forward. Ideally, I would like to add capacitors across upper IGBTs; not sure if this is needed and there are no PCB pads for that on the board.

mtwieg

Advanced Member level 6

Hopefully those changes don't degrade efficiency significantly. You would likely get better results with properly sized RC snubbers on the switching legs, as they will reduce the peak switching currents they absorb while still reducing the dv/dt of the switching nodes. Like Easy Peasy mentioned above, the footprints you have for those resistors might not be sufficient for the power they will dissipate though.

Anyways glad you managed to improve the situation, thanks for sharing.

Anyways glad you managed to improve the situation, thanks for sharing.

Easy peasy

Advanced Member level 6

generally 10nF caps are not placed directly across igbt's ( or mosfets ) as the turn on losses really go up

per the above a proper RC snubber should be considered.

a decent cap across each totem pole is however a good idea

is your sw freq 4kHz - as you wrote above, or 40kHz ?

per the above a proper RC snubber should be considered.

a decent cap across each totem pole is however a good idea

--- Updated ---

is your sw freq 4kHz - as you wrote above, or 40kHz ?

mike buba

Member level 3

Easy peasy

Advanced Member level 6

OK - at 4kHz you can get away with a lot more snubbing, say 4.7nF and 100 ohm across each switch

the power in the R will be approx, Psnub = C. V^2. F = 8 watts - so some serious power resistors needed ( not too inductive though ) - for 2.2 nF the power in the 100E = 3.7 watts - so better.

At the moment the lower devices are having to discharge the 10nF you placed there, for 650V on the cap each time the lower device turns on - the extra dissipation in the lower devices = 8.45W

( the peak current spike can easily be > 100A with just a cap ).

This peak current is a fairly narrow but quite high spike due to the cap being discharged by the device, ( these peak currents at turn on can cause premature device failure in some devices ) - with the 100E resistor as part of the snubber the current spike is limited to 650/100 = 6.5 amps, (x2 if you have a snubber across all devices). Proper snubbing will allow you to speed up the turn on a little bit and so reduce the turn on losses for the inverter load current - the turn off should always be pretty hard, e.g. Rturn-off = 10 ohms or less - as the turn off generates far less RF noise than the turn on.

Food for thought.

p.s. - what is the intended max power of the inverter ?

p.p.s. if those fuses shown are of the opposite polarity - glue a bit of card/phenolic board between them to stop accidental shorts - or better yet cover entirely - along with the separator - as it is no fun if these get touched by personnel or spanners or screwdrivers, or a metal wristwatch strap ...

the power in the R will be approx, Psnub = C. V^2. F = 8 watts - so some serious power resistors needed ( not too inductive though ) - for 2.2 nF the power in the 100E = 3.7 watts - so better.

At the moment the lower devices are having to discharge the 10nF you placed there, for 650V on the cap each time the lower device turns on - the extra dissipation in the lower devices = 8.45W

( the peak current spike can easily be > 100A with just a cap ).

This peak current is a fairly narrow but quite high spike due to the cap being discharged by the device, ( these peak currents at turn on can cause premature device failure in some devices ) - with the 100E resistor as part of the snubber the current spike is limited to 650/100 = 6.5 amps, (x2 if you have a snubber across all devices). Proper snubbing will allow you to speed up the turn on a little bit and so reduce the turn on losses for the inverter load current - the turn off should always be pretty hard, e.g. Rturn-off = 10 ohms or less - as the turn off generates far less RF noise than the turn on.

Food for thought.

p.s. - what is the intended max power of the inverter ?

--- Updated ---

p.p.s. if those fuses shown are of the opposite polarity - glue a bit of card/phenolic board between them to stop accidental shorts - or better yet cover entirely - along with the separator - as it is no fun if these get touched by personnel or spanners or screwdrivers, or a metal wristwatch strap ...

Last edited:

mike buba

Member level 3

I can add resistors in series with the capacitors. There is space for the lower IGBTs.OK - at 4kHz you can get away with a lot more snubbing, say 4.7nF and 100 ohm across each switch

the power in the R will be approx, Psnub = C. V^2. F = 8 watts - so some serious power resistors needed ( not too inductive though ) - for 2.2 nF the power in the 100E = 3.7 watts - so better.

At the moment the lower devices are having to discharge the 10nF you placed there, for 650V on the cap each time the lower device turns on - the extra dissipation in the lower devices = 8.45W

( the peak current spike can easily be > 100A with just a cap ).

Not sure how to add it to the upper. I am not seeing any accessible place.

This is my next step. To add Schottky diode to separate Rgon and Rgoff.This peak current is a fairly narrow but quite high spike due to the cap being discharged by the device, ( these peak currents at turn on can cause premature device failure in some devices ) - with the 100E resistor as part of the snubber the current spike is limited to 650/100 = 6.5 amps, (x2 if you have a snubber across all devices). Proper snubbing will allow you to speed up the turn on a little bit and so reduce the turn on losses for the inverter load current - the turn off should always be pretty hard, e.g. Rturn-off = 10 ohms or less - as the turn off generates far less RF noise than the turn on.

Pout = 3 kW at 3x400 Vac, line current = 4.3 Aacrmsp.s. - what is the intended max power of the inverter ?

Yes, they are in +DC and -DC branch. Thanks for the advice. Will dop.p.s. if those fuses shown are of the opposite polarity - glue a bit of card/phenolic board between them to stop accidental shorts - or better yet cover entirely - along with the separator - as it is no fun if these get touched by personnel or spanners or screwdrivers, or a metal wristwatch strap ...

mike buba

Member level 3

Another update:

Note I have not run the converter after adding the Schottky diode to see the effects of the noise. I have run it only with both Schottky diode and RC snubber.

With RC snubber across each MOSFET (2200 pF, 120 Ohm)

With only C snubber in lower MOSFETs (0.01 µF)

If I put back a 0.01 µF capacitor (which in the previous case showed better noise reduction performance) the power will increase, but even now the resistor gets hot to touch (approx. 50 DegC). I can use smaller resistors, but then I read resistance should be >= Vdc/Idc (650 / 5 = 130 Ohm).

This is what the installation looks like... the best I could think of to get RC snubber across both upper and lower MOSFET. PCB has pads for only lower MOSFET RC snubber, and it is for SMD components.

This is how one of the previous installations looked like with only RC snubber across lower MOSFETs; but then I couldn't think of the way to add it across upper.

- I added Schottky diode to MOSFET driver board so that Rgon is 23.5 Ohm and Rgoff is 10 Ohm

- I added an RC snubber circuit to every MOSFET, R = 120 Ohm, 4 W, C = 2200 pF, 2 kV

Note I have not run the converter after adding the Schottky diode to see the effects of the noise. I have run it only with both Schottky diode and RC snubber.

With RC snubber across each MOSFET (2200 pF, 120 Ohm)

With only C snubber in lower MOSFETs (0.01 µF)

If I put back a 0.01 µF capacitor (which in the previous case showed better noise reduction performance) the power will increase, but even now the resistor gets hot to touch (approx. 50 DegC). I can use smaller resistors, but then I read resistance should be >= Vdc/Idc (650 / 5 = 130 Ohm).

This is what the installation looks like... the best I could think of to get RC snubber across both upper and lower MOSFET. PCB has pads for only lower MOSFET RC snubber, and it is for SMD components.

This is how one of the previous installations looked like with only RC snubber across lower MOSFETs; but then I couldn't think of the way to add it across upper.

Last edited:

Easy peasy

Advanced Member level 6

No, no, no, respectfully, the snubbers need to be soldered directly onto the D & S pins, soldering the R direct to the Drain allows a measure of heatsinking for the R ( this works ), short leads .. ! i.e. a short as you can absolutely make them, i.e. Cap up ( on its side ) and R down to Drain ... - so the net loop area of the two bits is quite small ...!

mike buba

Member level 3

Should I then keep 2.2 nF or change to 10 nF or even increase to 20 nFNo, no, no, respectfully, the snubbers need to be soldered directly onto the D & S pins, soldering the R direct to the Drain allows a measure of heatsinking for the R ( this works ), short leads .. ! i.e. a short as you can absolutely make them, i.e. Cap up ( on its side ) and R down to Drain ... - so the net loop area of the two bits is quite small ...!

In that case, is 120 Ohm okay, or should I change that as well? 10 nF showed slightly better noise reduction when comparing oscillograms, but power will increase proportionally

I can solder RC snubber on PCB pads for lower MOSFETs as shown in the last picture in my previous post. For upper not sure how to do that yet, especially since all has to go under MOSFET driver.

Last edited:

Easy peasy

Advanced Member level 6

keep to 2.2nf at this stage, as for the high side mosfets, if it has to go under the driver - so be it.

once the subbers are in place you need a decent high BW scope and probes to look at the mid point - zoom into to 20nS / div or whatever gives you a good look at the transition each way - and post.

--- Updated ---

once the subbers are in place you need a decent high BW scope and probes to look at the mid point - zoom into to 20nS / div or whatever gives you a good look at the transition each way - and post.

- Status

- Not open for further replies.

Similar threads

-

Reducing noise in buck converter powering push pull inverter

- Started by Bruno5234

- Replies: 33

-

-

-

-