HariHerekar

Newbie level 6

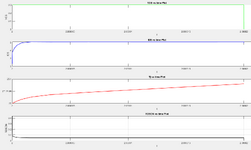

Hey all, just wanted clearing up on this concept. I have a range of VDS vs IDS values I obtained by testing the device GS66508B on a Keysight curve tracer.

To find its RDSON, is it as simple as VDS/IDS ? I know that values must be in the linear region where VGS-Vth>VDS, but are there any extra parameters i must keep in mind while finding the RDSON for a GaN FET ?

Also, i know the equivalent circuit for the small signal behaviour in the saturation region is a voltage dep. current source, but is this behavior valid for large signals as well ?

If so, is VDS/IDS in saturation also an RDSON ?

To find its RDSON, is it as simple as VDS/IDS ? I know that values must be in the linear region where VGS-Vth>VDS, but are there any extra parameters i must keep in mind while finding the RDSON for a GaN FET ?

Also, i know the equivalent circuit for the small signal behaviour in the saturation region is a voltage dep. current source, but is this behavior valid for large signals as well ?

If so, is VDS/IDS in saturation also an RDSON ?