BrownieHaHa

Newbie level 6

Hi everyone, I have encountered some issues:

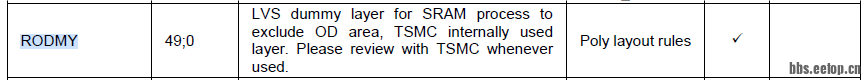

1. In the SRAM layout rules TSMCN28 HPCP process, there is a rule called RODMY, as seen in Figures 1 and 2. I do not quite understand this rule.

3. Similarly, in the SRAM layout from the TSMC Memory Compiler, there are layers numbered 30;21 and 30;22, named CO_TESTB and CO_TESTC, respectively. Obviously, these are related to Contacts. These two special Contacts cover/partially cover the special Contact between the gate and the active region of the SRAM, as shown in Figure 3. I did not find the function and rules for these two layers in the TSMC CLDR002 and CLCL054 documents.

1. In the SRAM layout rules TSMCN28 HPCP process, there is a rule called RODMY, as seen in Figures 1 and 2. I do not quite understand this rule.

Figure 1

Figure 2

2. In the SRAM layout from the TSMC Memory Compiler, there are rectangular Contacts (which are crucial for size reduction), you can see these 2 rectangular contacts in Figure 2. I did not find the related DRC rules for these rectangular via holes in the TSMC CLDR002 and CLCL054 documents.Figure 2

3. Similarly, in the SRAM layout from the TSMC Memory Compiler, there are layers numbered 30;21 and 30;22, named CO_TESTB and CO_TESTC, respectively. Obviously, these are related to Contacts. These two special Contacts cover/partially cover the special Contact between the gate and the active region of the SRAM, as shown in Figure 3. I did not find the function and rules for these two layers in the TSMC CLDR002 and CLCL054 documents.

Figure 3

I look forward to your guidance!