xiaofeixia

Junior Member level 3

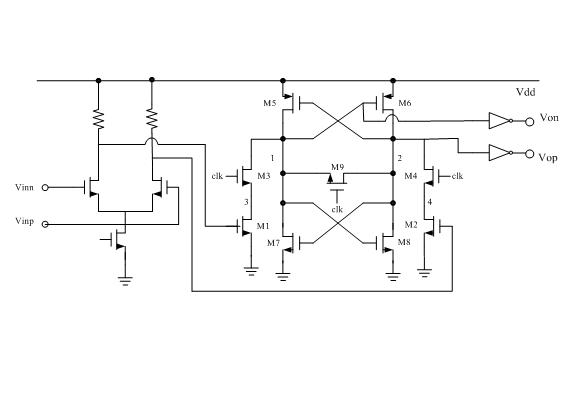

comparater

i simulated a high-speed latched comparator with preamplifier in tsmc 018 process, when i simulate the input offset i use the pch_mis and nmos_mis model(include delta(Avt,w,l,tox)) for only input and latch mosfets

but the results show a high offset:

mean = -11.1877m varian = 13.1798m

sigma = 114.8033m avgdev = 83.3351m

who can help why? thanks

i simulated a high-speed latched comparator with preamplifier in tsmc 018 process, when i simulate the input offset i use the pch_mis and nmos_mis model(include delta(Avt,w,l,tox)) for only input and latch mosfets

but the results show a high offset:

mean = -11.1877m varian = 13.1798m

sigma = 114.8033m avgdev = 83.3351m

who can help why? thanks