FreshmanNewbie

Advanced Member level 1

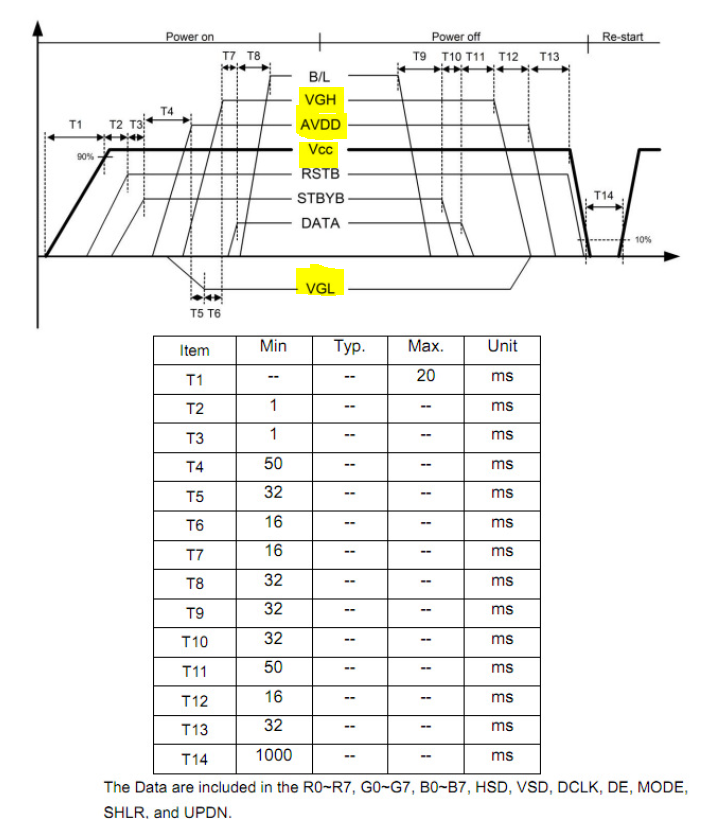

I have a TFT whose power sequencing is given below:

VGH (typ is 19V), VGL(typ is -10V), AVDD (typ is 12.4V), VCC (typ is 3.3V), are power supplies for the TFT.

Mentioned are the typ values required.

Would the TI part help to satisfy the power sequencing of the above TFT?

As far as I checked, in the TI datasheet, I plan to use as below, Vo1 for AVDD, Vo2 for VGL, Vo3 for VGH and Vo4 for Vcc.

Going through the power-up sequencing mentioned on page 12, section 7.4.1, it seems the TI part won't help with the power sequencing of the TFT.

Can someone confirm whether my understanding is correct? If yes, any workarounds, or suggestions possible?

VGH (typ is 19V), VGL(typ is -10V), AVDD (typ is 12.4V), VCC (typ is 3.3V), are power supplies for the TFT.

Mentioned are the typ values required.

Would the TI part help to satisfy the power sequencing of the above TFT?

As far as I checked, in the TI datasheet, I plan to use as below, Vo1 for AVDD, Vo2 for VGL, Vo3 for VGH and Vo4 for Vcc.

Going through the power-up sequencing mentioned on page 12, section 7.4.1, it seems the TI part won't help with the power sequencing of the TFT.

Can someone confirm whether my understanding is correct? If yes, any workarounds, or suggestions possible?