afujian

Member level 4

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

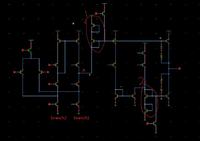

Right!If a 2*Vth shift is generated,there should be some current flow through the diode-connected transistors.

... the branch1 and branch2 are totally matched,so the current of the two branches should be matched too,hence,no current should be flow through the transistors in the circle 1,and no shift should be generated,right?