melkord

Full Member level 3

Hi,

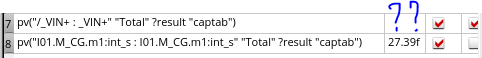

while I can put node capacitance of instances to the output, I cannot put the node capacitance of the node at the top level to the output.

Is there a way to do that without creating a symbol for my top level and then instantiate it (assuming it works that way, I have not tried it) ?

while I can put node capacitance of instances to the output, I cannot put the node capacitance of the node at the top level to the output.

Is there a way to do that without creating a symbol for my top level and then instantiate it (assuming it works that way, I have not tried it) ?