cupoftea

Advanced Member level 6

Hi,

Do you agree, the Pushpull SMPS must generally be used with an active snubber to regenerate primary side leakage inductance energy?

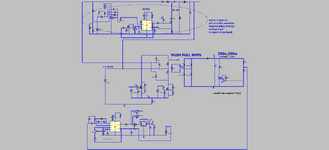

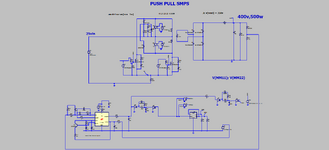

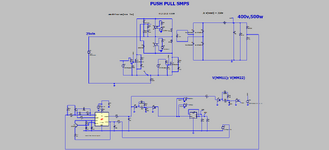

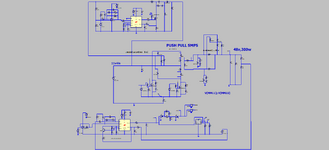

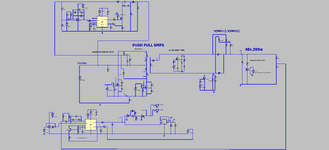

The attached (LTspice and PNG schems) shows a 200W pushpull with vin = 11.4V, and Vout = 350V, and an active snubber using a SEPIC converter. The SEPIC is not an option. It is rather a must.

Do you agree, when the Pushpull SMPS is used it is almost always used in cases where input voltage is low. (Due to its problem of suffering a voltage of 2xVin on its primary FETs).

So as such, it is often used when input current is high. (Since if output power is high, and Vin is low, then input current must be high).

This in itself brings a problem. Because..The Pushpull SMPS does not recycle transformer leakage energy back to the input. (unlike the Two Transistor Forward, the Half Bridge, the Full Bridge, the Phase shift full bridge and the LLC). As such, the Push pull is somewhat a pariah of SMPS’s.

When the input current is high, then so too is the energy stored in the transformer leakage inductance. The Pushpull has no way of regenerating this energy. Its only defence is to use interleave winding. However, since a pushpull has two primary “half” coils which conduct consecutively, then this means that even with a single_turn_secondary_with_FWB, there would be five coils in the pushpull transformer….a “sandwich” of sec_pri1_sec_pri2_sec…with the “sec” bits each being series connected to make the overall single secondary coil. This is the simplest way to get “Interleave” winding done with a pushpull. However, really the two primary halves need to also be interleaved with each other…but doing this makes the transistor way too expensive.

If the two primary halves are not well coupled with each other, then there will be a higher overall flux in the transformer, (since each coils conduction demagnetises [resets] the others flux) and this will put you nearer to saturation…decreasing the needed margin before saturation.

So do you agree, your only realistic option with pushpull is to go sec_pri1_sec_pri2_sec, accept that you have a high leakage inductance problem, and then just use a SEPIC based active snubber to recycle the leakage energy? (A resistive snubber would be way too dissipative for pushpull).

Do you agree, the Pushpull SMPS must generally be used with an active snubber to regenerate primary side leakage inductance energy?

The attached (LTspice and PNG schems) shows a 200W pushpull with vin = 11.4V, and Vout = 350V, and an active snubber using a SEPIC converter. The SEPIC is not an option. It is rather a must.

Do you agree, when the Pushpull SMPS is used it is almost always used in cases where input voltage is low. (Due to its problem of suffering a voltage of 2xVin on its primary FETs).

So as such, it is often used when input current is high. (Since if output power is high, and Vin is low, then input current must be high).

This in itself brings a problem. Because..The Pushpull SMPS does not recycle transformer leakage energy back to the input. (unlike the Two Transistor Forward, the Half Bridge, the Full Bridge, the Phase shift full bridge and the LLC). As such, the Push pull is somewhat a pariah of SMPS’s.

When the input current is high, then so too is the energy stored in the transformer leakage inductance. The Pushpull has no way of regenerating this energy. Its only defence is to use interleave winding. However, since a pushpull has two primary “half” coils which conduct consecutively, then this means that even with a single_turn_secondary_with_FWB, there would be five coils in the pushpull transformer….a “sandwich” of sec_pri1_sec_pri2_sec…with the “sec” bits each being series connected to make the overall single secondary coil. This is the simplest way to get “Interleave” winding done with a pushpull. However, really the two primary halves need to also be interleaved with each other…but doing this makes the transistor way too expensive.

If the two primary halves are not well coupled with each other, then there will be a higher overall flux in the transformer, (since each coils conduction demagnetises [resets] the others flux) and this will put you nearer to saturation…decreasing the needed margin before saturation.

So do you agree, your only realistic option with pushpull is to go sec_pri1_sec_pri2_sec, accept that you have a high leakage inductance problem, and then just use a SEPIC based active snubber to recycle the leakage energy? (A resistive snubber would be way too dissipative for pushpull).