yefj

Advanced Member level 5

Hello, generally when i design an RF power divider its always about the impedance of the lines(Suppuse its T-junction).i do a champers and formulas to get a good insertion loss and return loss.

my line width is always an impedance calculation.

Here i have a different kind of situation. I have a demand to deliver 3A and 6V to a drain for 5 devices from a single source.

my pulse is 50u with 35% duty cycle and 20nsec rise and fall time

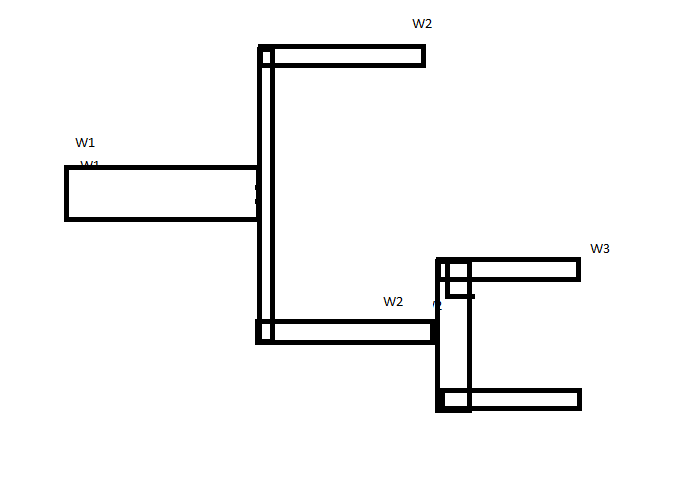

Using formulas i have found w1 w2 w3 :

W1=100mil 13 degree rise for 15A

W2=40mil 12.6 degree rise for 7.5A

etc..

I have the following problems:

1.my line width are not impedances but the width which could handle the current pulse.

How to construct the current divider for such case?

2.i need also need to deliver the square pulse intact, how do i consider the delivering the spectral data safely to the destination?

3.given my signal pulse how do i know what bandwidth to consider as containing most of its spectral pulse data?

4.I have SMA connector of 50 Ohms delivering this pulse,so once again how do i match the 50Ohm connector to the main artery trace which has to be 100mils just so it could wistand the current. 100 mils is not 50 Ohms to the signal.

Thanks.

my line width is always an impedance calculation.

Here i have a different kind of situation. I have a demand to deliver 3A and 6V to a drain for 5 devices from a single source.

my pulse is 50u with 35% duty cycle and 20nsec rise and fall time

Using formulas i have found w1 w2 w3 :

W1=100mil 13 degree rise for 15A

W2=40mil 12.6 degree rise for 7.5A

etc..

I have the following problems:

1.my line width are not impedances but the width which could handle the current pulse.

How to construct the current divider for such case?

2.i need also need to deliver the square pulse intact, how do i consider the delivering the spectral data safely to the destination?

3.given my signal pulse how do i know what bandwidth to consider as containing most of its spectral pulse data?

4.I have SMA connector of 50 Ohms delivering this pulse,so once again how do i match the 50Ohm connector to the main artery trace which has to be 100mils just so it could wistand the current. 100 mils is not 50 Ohms to the signal.

Thanks.

Last edited: