doenisz

Junior Member level 2

I'm looking to minimize the frequency variation of an on-chip ring oscillator running at 2MHz, through using either an LDO as its supply voltage, or current-starving it with a current coming from a PTAT current source, coming from a constant-gm core

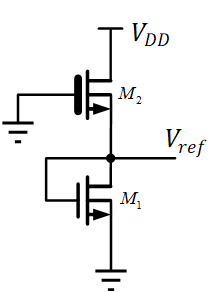

I simulated the ring oscillator with both structures having the same power consumption to make the comparison more fair. I generated the VREF for the LDO as a simple 2T voltage reference

, because I'm on a power budget. Keep in mind, this circuit itself has some PVT and supply variation.

, because I'm on a power budget. Keep in mind, this circuit itself has some PVT and supply variation.

To my surprise, the PTAT current starving actually gave me better PVT insensitivity compared to LDO and I cannot really justify it with theory.

The only explanation I could come up with is that the resistance in the PTAT core tracks the PVT in the same way as the NMOS/PMOS in the ring oscillator.

I would appreciate it if you could please help me understand this better. I'd like to repeat, PTAT core and the LDO runs at the same power, so LDO bandwidth is not too great so it might be related to its settling too.

Best.

I simulated the ring oscillator with both structures having the same power consumption to make the comparison more fair. I generated the VREF for the LDO as a simple 2T voltage reference

To my surprise, the PTAT current starving actually gave me better PVT insensitivity compared to LDO and I cannot really justify it with theory.

The only explanation I could come up with is that the resistance in the PTAT core tracks the PVT in the same way as the NMOS/PMOS in the ring oscillator.

I would appreciate it if you could please help me understand this better. I'd like to repeat, PTAT core and the LDO runs at the same power, so LDO bandwidth is not too great so it might be related to its settling too.

Best.