Porsche

Member level 1

Hello everyone!

Recently I was researching my PSFB converter and came across a phenomenon that was unclear to me.

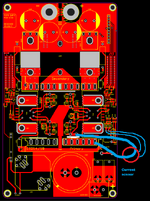

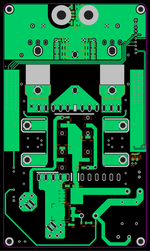

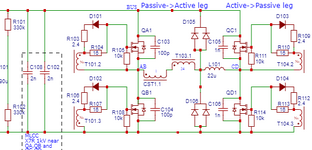

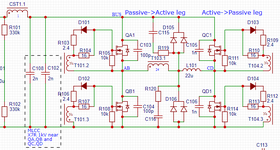

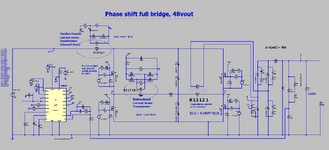

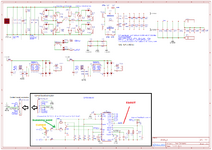

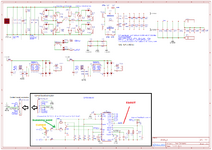

Please see schematic, it is classical PCMC PSFB. The current sense transformer (CST1) placed in sires with main power transformer T103.

I configured error amplifier as a buffer such that a pot RP1 controls EAOUT voltage thus an effective duty cycle can be controlled manually by tuning RP1.

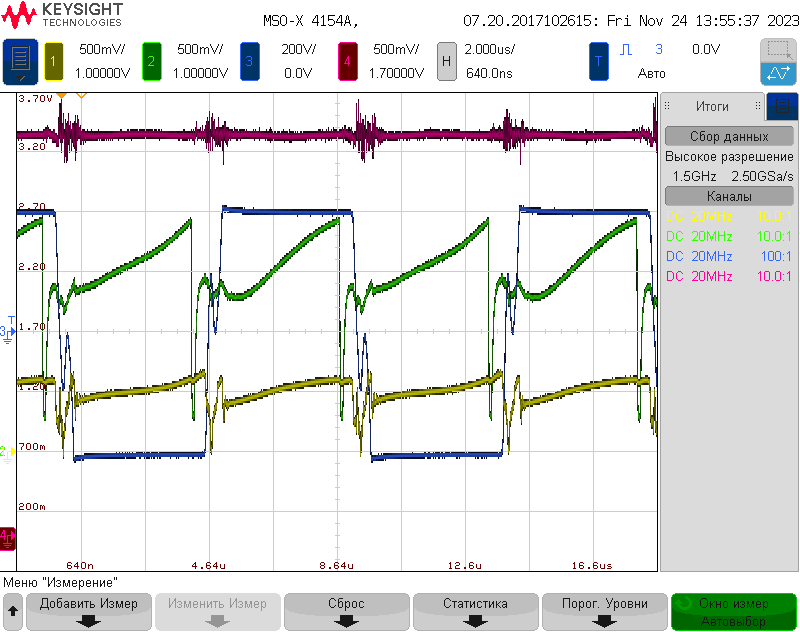

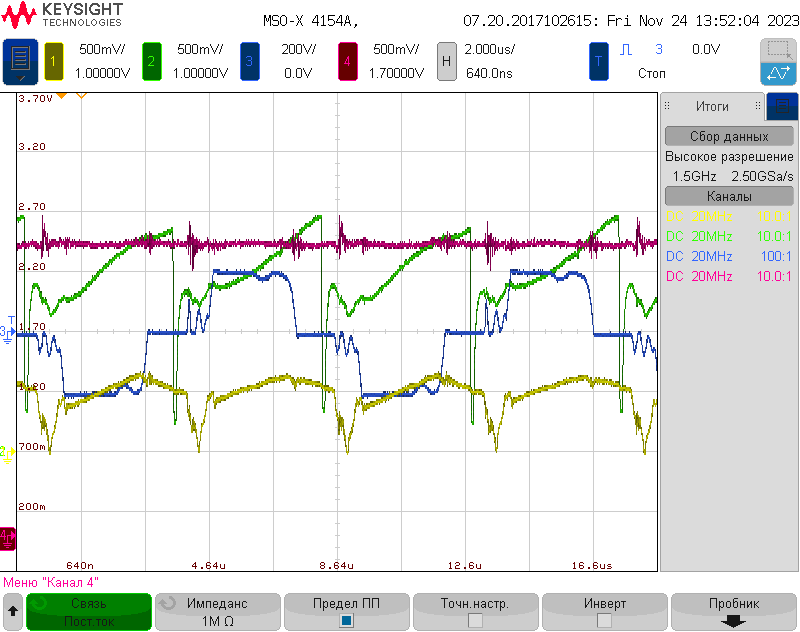

I noticed that when EAOUT (Red) signal reaches Sum(Green) signal, the shape of the current signal (Yellow) was greatly distorted. In the absence of "stabilization", the current shape looks normal and is almost the same for each cycle.

Please see following waveforms.

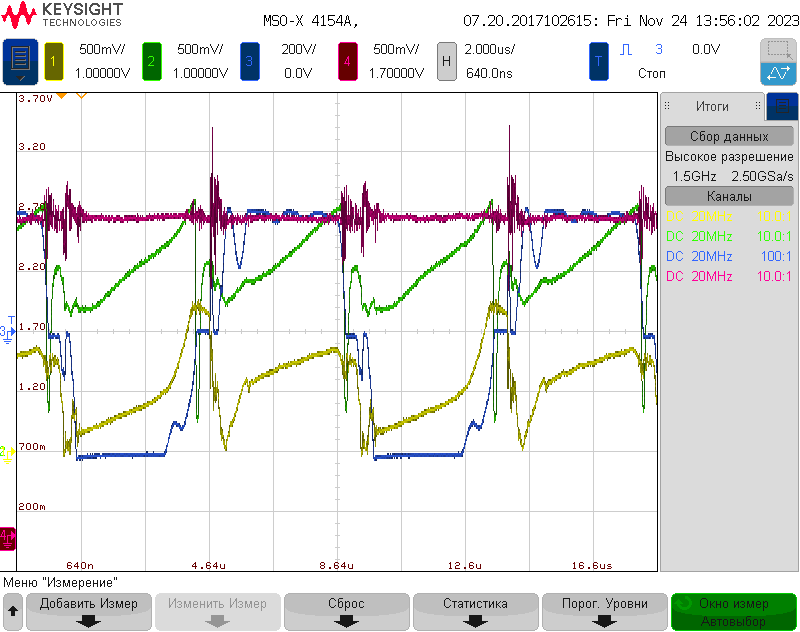

EAOUT (Red) has not reached sum signal (Green) at the ramp pin yet, thus maximum duty cycle observed (Blue - Tx's primary voltage). Current(Yellow) looks normal.

EAOUT(red) just touched the sum signal (green) and the current waveform fell apart. Nevertheless duty cycle has been limited (blue - the voltage on the transformer primary).

This kind of current shape distortion is very similar to the saturation phenomenon of the main transformer. But I have no idea how it is possible?

In the worst scenario, the calculated amplitude of the transformer magnetic flux density does not exceed +/-150 mT, which is almost 2 times less than the saturation limit of the N87 material (320 mT). The only reason I can think of for this, is that there is some DC current present in the transformer which pushes the hysteresis loop closer to saturation and then my +- 150 mT hits saturation point.

To confirm my theory I added a paper gap (0.1 mm) to the main transformer and indeed the current shape was not distorted anymore.

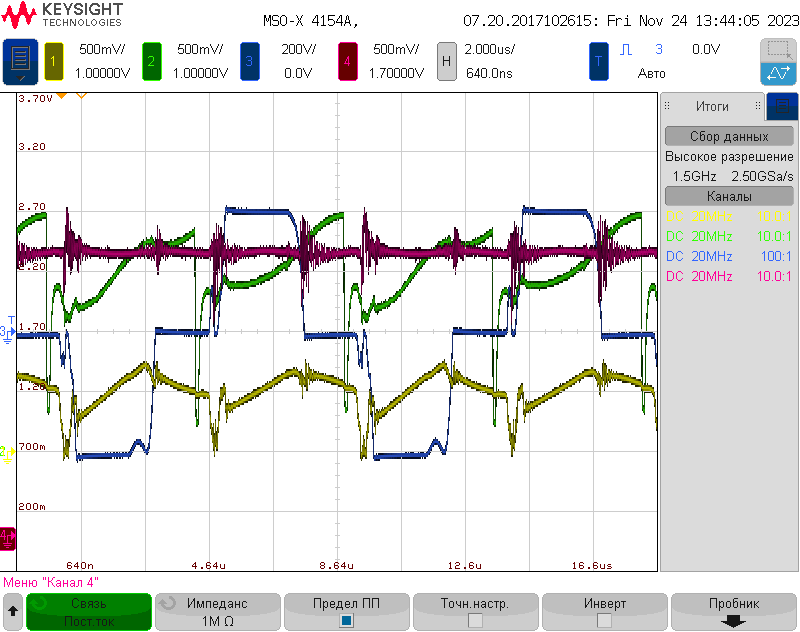

EAOUT (Red) has not reached sum signal (Green) at the ramp pin yet, thus maximum duty cycle observed (Blue - Tx's primary voltage). Current(Yellow) looks normal.

EAOUT(red) touched the sum signal (green) and the current waveform O.K. thanks to air gap. Duty cycle has been limited (blue - the voltage on the transformer primary).

If the input voltage reduced under 200V it is possible to obtain a proper operation even without a gap in the transformer core.

I always thought that PCMC would prevent any core flux imbalance, but it seems it's not that simple.

Despite the fact that the gap in the transformer helped improve the situation, I would like to understand the reason for this process. I think that I have not solved the problem yet but just pushed it to a higher power level, which could lead to failure at extreme operating conditions. In addition, I have seen many appnotes in which the transformer has no gap at all.

Apart from introducing a gap, what is the correct way to solve this problem?

My magnetics data:

Primary transformer (T103) - ETD54 N87

Np = 24 Ns = 4

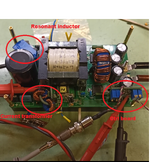

Resonant inductor (L101) - gapped RM 12 N87

N = 12 L = 22uH

Output inductor (L201) - APH40P60

Ae=1.072cm^2

Al=81nH/turn^2

le = 9.84cm

Bsat=1.5T

N=12

L = 10 uH (at the nominal load current)

Nominal input voltage 400VDC

Nominal power level 1800W

Fsw = 108kHz

Recently I was researching my PSFB converter and came across a phenomenon that was unclear to me.

Please see schematic, it is classical PCMC PSFB. The current sense transformer (CST1) placed in sires with main power transformer T103.

I configured error amplifier as a buffer such that a pot RP1 controls EAOUT voltage thus an effective duty cycle can be controlled manually by tuning RP1.

I noticed that when EAOUT (Red) signal reaches Sum(Green) signal, the shape of the current signal (Yellow) was greatly distorted. In the absence of "stabilization", the current shape looks normal and is almost the same for each cycle.

Please see following waveforms.

EAOUT (Red) has not reached sum signal (Green) at the ramp pin yet, thus maximum duty cycle observed (Blue - Tx's primary voltage). Current(Yellow) looks normal.

EAOUT(red) just touched the sum signal (green) and the current waveform fell apart. Nevertheless duty cycle has been limited (blue - the voltage on the transformer primary).

This kind of current shape distortion is very similar to the saturation phenomenon of the main transformer. But I have no idea how it is possible?

In the worst scenario, the calculated amplitude of the transformer magnetic flux density does not exceed +/-150 mT, which is almost 2 times less than the saturation limit of the N87 material (320 mT). The only reason I can think of for this, is that there is some DC current present in the transformer which pushes the hysteresis loop closer to saturation and then my +- 150 mT hits saturation point.

To confirm my theory I added a paper gap (0.1 mm) to the main transformer and indeed the current shape was not distorted anymore.

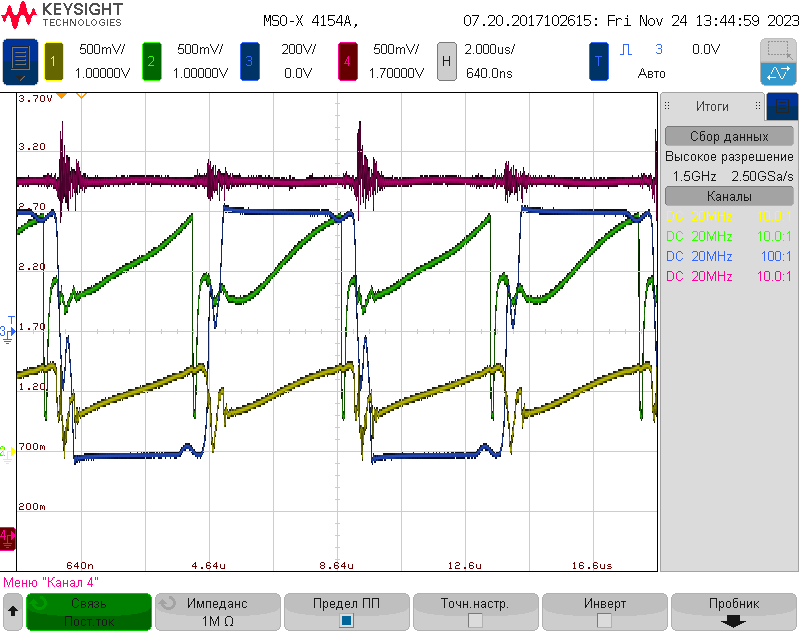

EAOUT (Red) has not reached sum signal (Green) at the ramp pin yet, thus maximum duty cycle observed (Blue - Tx's primary voltage). Current(Yellow) looks normal.

EAOUT(red) touched the sum signal (green) and the current waveform O.K. thanks to air gap. Duty cycle has been limited (blue - the voltage on the transformer primary).

If the input voltage reduced under 200V it is possible to obtain a proper operation even without a gap in the transformer core.

I always thought that PCMC would prevent any core flux imbalance, but it seems it's not that simple.

Despite the fact that the gap in the transformer helped improve the situation, I would like to understand the reason for this process. I think that I have not solved the problem yet but just pushed it to a higher power level, which could lead to failure at extreme operating conditions. In addition, I have seen many appnotes in which the transformer has no gap at all.

Apart from introducing a gap, what is the correct way to solve this problem?

My magnetics data:

Primary transformer (T103) - ETD54 N87

Np = 24 Ns = 4

Resonant inductor (L101) - gapped RM 12 N87

N = 12 L = 22uH

Output inductor (L201) - APH40P60

Ae=1.072cm^2

Al=81nH/turn^2

le = 9.84cm

Bsat=1.5T

N=12

L = 10 uH (at the nominal load current)

Nominal input voltage 400VDC

Nominal power level 1800W

Fsw = 108kHz