BojackHorseman

Newbie level 6

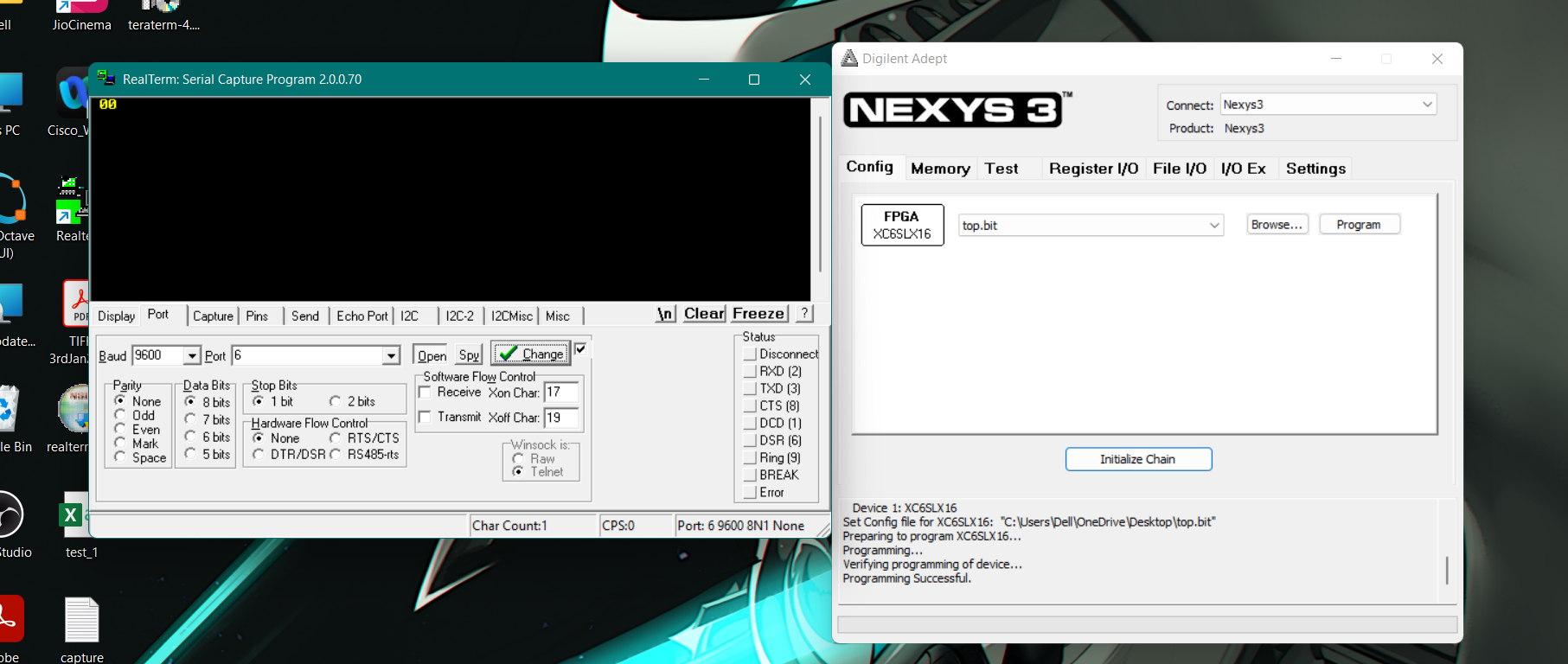

I am trying to send a 1 byte of data from my Nexys 3 board to my PC using UART communication. But the problem is whenever I try to view the data on Real Term no matter my input(hard coded into the code or given via switches) the transmitted data always shows 0. I checked by simulating the entire thing but there, the code was working as expected.

Can someone help me in solving this bug.

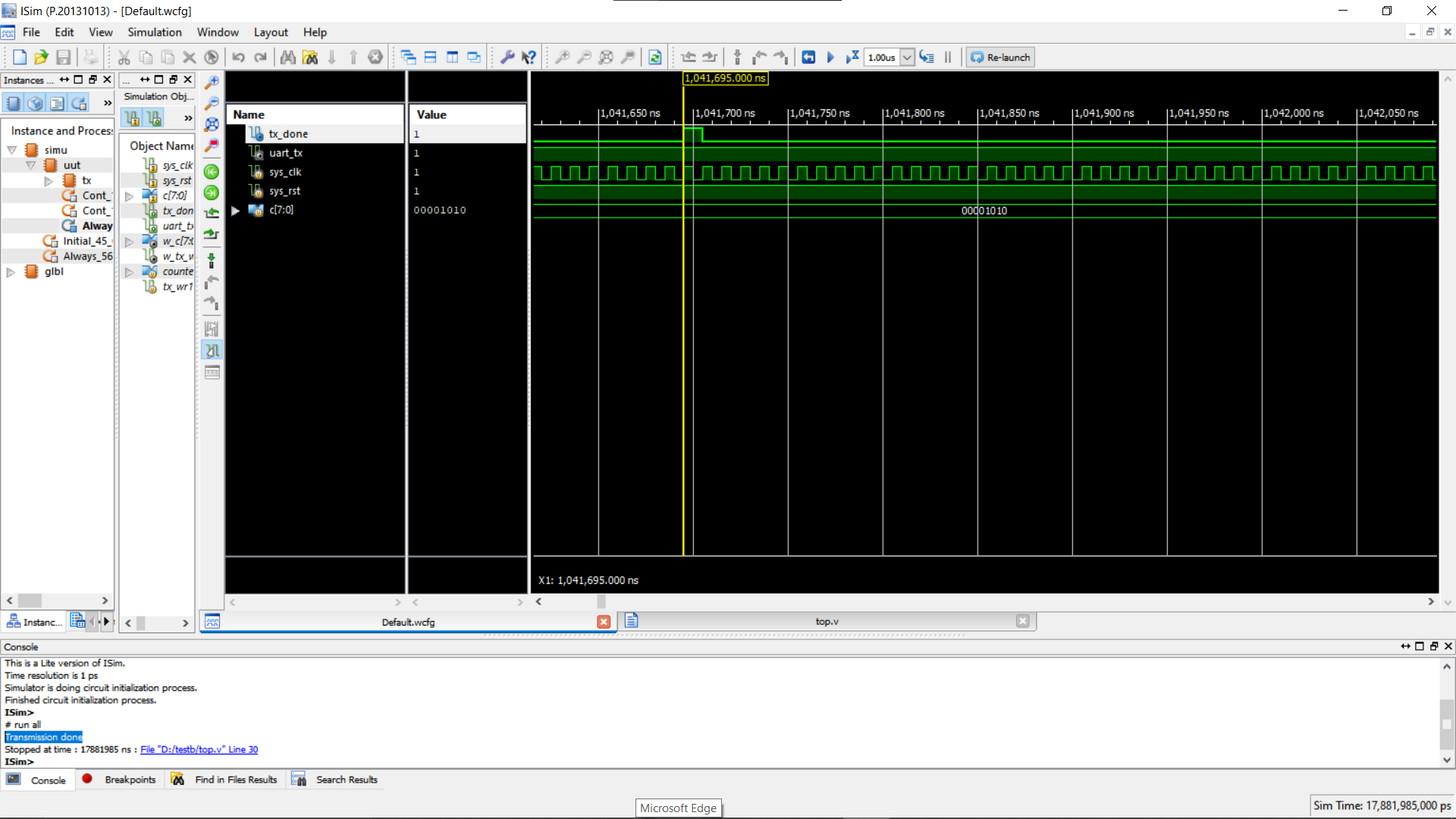

Simulation Output:

tx_done indicates that the transmission of 1 byte has been done successfully

Output as shown on the RealTerm window. No matter the input, the transmitted value remains the same

Can someone help me as to why this is happening ?

Can someone help me in solving this bug.

Code:

Code:

`timescale 1ns / 1ps

module top( input sys_clk,

input sys_rst,

input [7:0] c,

output tx_done,

output uart_tx

);

wire [7:0] w_c;

assign w_c = c;

reg [31:0] counter;

reg tx_wr1;

wire w_tx_wr;

assign w_tx_wr = tx_wr1;

uart_tx tx(

.sys_clk(sys_clk),

.sys_rst(sys_rst),

.tx_data(w_c),

.tx_wr(w_tx_wr),

.tx_done(tx_done),

.uart_tx(uart_tx)

);

always @(posedge sys_clk) begin

if(sys_rst == 0 ) begin

counter <= 32'd0;

tx_wr1<= 1'd0;

end

else begin

counter <= counter + 32'd1;

if (counter == 2) begin

tx_wr1 <= 1'd1;

end

else tx_wr1 <= 1'd0;

end

end

endmodule

////////////////////////////////////////////////////////////////////////////////////

module uart_tx(

input sys_rst,

input sys_clk,

output reg uart_tx,

input [7:0] tx_data,

input tx_wr,

output reg tx_done

);

//-----------------------------------------------------------------

// enable16 generator

//-----------------------------------------------------------------

reg [15:0] enable16_counter;

reg [15:0] divisor;

parameter [15:0] BAUD = 16'd651;

wire enable16;

assign enable16 = (enable16_counter == 16'd0);

always @(posedge sys_clk)

begin

if(sys_rst==0) begin

enable16_counter <= divisor - 16'b1;

divisor <= BAUD;

end

else begin

enable16_counter <= enable16_counter - 16'd1;

if(enable16)

enable16_counter <= divisor - 16'b1;

end

end

//-----------------------------------------------------------------

// UART TX Logic

//-----------------------------------------------------------------

reg tx_busy;

reg [3:0] tx_bitcount;

reg [3:0] tx_count16;

reg [7:0] tx_reg;

always @(posedge sys_clk) begin

if(sys_rst==0) begin

tx_done <= 1'b0;

tx_busy <= 1'b0;

uart_tx <= 1'b1;

end else begin

tx_done <= 1'b0;

if(tx_wr) begin

tx_reg <= tx_data;

tx_bitcount <= 4'd0;

tx_count16 <= 4'd1;

tx_busy <= 1'b1;

uart_tx <= 1'b0;

`ifdef SIMULATION

$display("UART: %c", tx_data);

`endif

end else if(enable16 && tx_busy) begin

tx_count16 <= tx_count16 + 4'd1;

if(tx_count16 == 4'd0) begin

tx_bitcount <= tx_bitcount + 4'd1;

if(tx_bitcount == 4'd8) begin

uart_tx <= 1'b1;

end else if(tx_bitcount == 4'd9) begin

uart_tx <= 1'b1;

tx_busy <= 1'b0;

tx_done <= 1'b1;

$display("Transmission done");

end else begin

uart_tx <= tx_reg[0];

tx_reg <= {1'b0, tx_reg[7:1]};

end

end

end

end

end

endmodule

////////////////////////TestBench///////////////////////////////////////////////////

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 23:30:56 01/03/2023

// Design Name: top

// Module Name: D:/testb/simu.v

// Project Name: testb

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: top

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module simu;

// Inputs

reg sys_clk;

reg sys_rst;

reg [7:0] c;

// Outputs

wire tx_done;

wire uart_tx;

// Instantiate the Unit Under Test (UUT)

top uut (

.sys_clk(sys_clk),

.sys_rst(sys_rst),

.c(c),

.tx_done(tx_done),

.uart_tx(uart_tx)

);

initial begin

// Initialize Inputs

sys_clk = 0;

sys_rst = 0;

c = 0;

// Wait 100 ns for global reset to finish

#100 sys_rst = 1;

c = 10 ;

// Add stimulus here

end

always #5 sys_clk = ~sys_clk;

endmoduleSimulation Output:

tx_done indicates that the transmission of 1 byte has been done successfully

Output as shown on the RealTerm window. No matter the input, the transmitted value remains the same

Can someone help me as to why this is happening ?