newbie2023

Newbie level 4

Hi everyone,

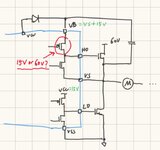

I'm studying design a moto driver circuit. I feel confused about how to choose the devices.

If the bus voltage = 40V, and the Vbs = 15V. Is the 16V nldmos/pldmos(BV=18V@MIN,25@TYP)enough for my design?

Or I should choose 60V devices which is greater than 40V + 15V ?

Thanks a lot!

I'm studying design a moto driver circuit. I feel confused about how to choose the devices.

If the bus voltage = 40V, and the Vbs = 15V. Is the 16V nldmos/pldmos(BV=18V@MIN,25@TYP)enough for my design?

Or I should choose 60V devices which is greater than 40V + 15V ?

Thanks a lot!