yefj

Advanced Member level 5

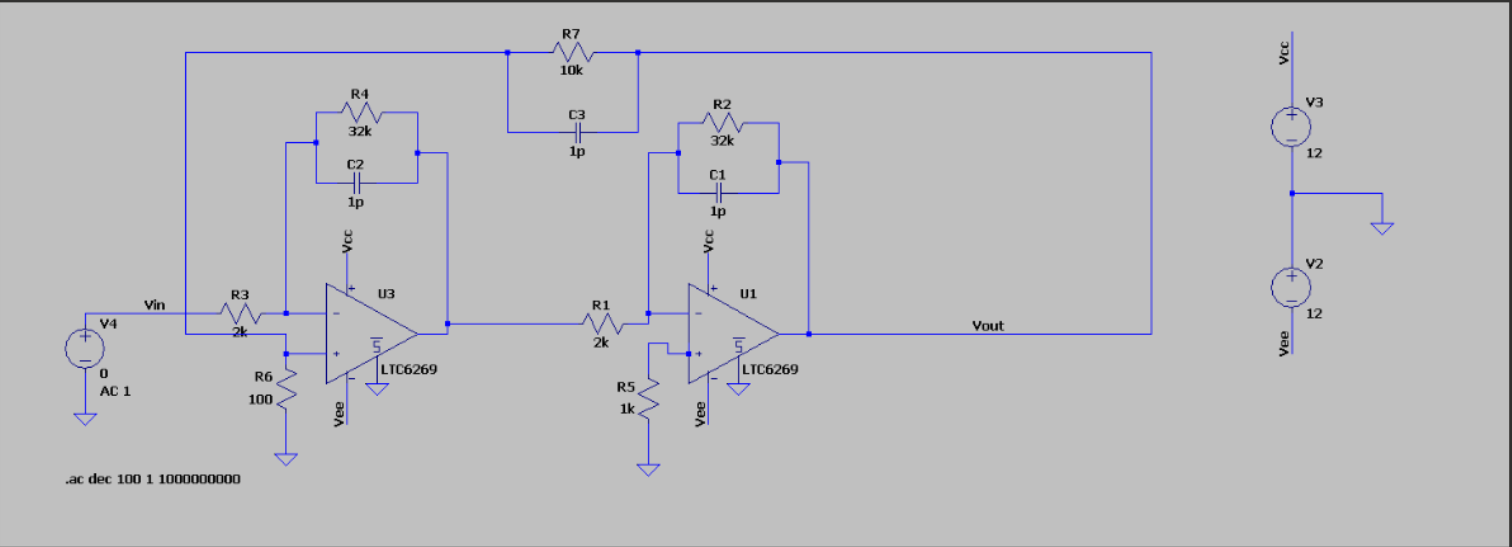

Hello i have a circuit shown bellow,as you can see my feedback line crossed the Vin line.

Is there some method of routing on how to overcome this obsticle?

Thanks.

Is there some method of routing on how to overcome this obsticle?

Thanks.