krazyfencer

Junior Member level 2

- Joined

- Aug 5, 2013

- Messages

- 23

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Location

- East Coast, USA

- Activity points

- 266

Hello,

I'm just starting out, so tell me if I am not saying this right. As I understand it (based on other posts), you can't depend upon the initial value of a flip flop. I have a set of jk flipflops with set/reset pins (CD4027B) and I wanted to know if the power-on-reset logic that I made makes sense.

1) is it true that you can't depend upon the initial value of a flip flop, or is this chip or technology (cmos vs ttl) dependent?

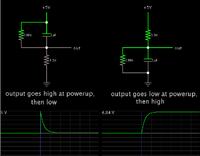

2) here is a falstad link to my por design (sort of, it is a bit simplified because the jk in falstad doesn't have set/reset pins and my actual project uses multiple jks chained together and fed from a 555). The wire hanging after the capacitor is meant to feed the reset pin.

The thing that has me sketched out is the connection from the transistor emitter back to it's base. It seems to work in falstad, but I'm wondering if anyone knows if this is insane and if there is an easier way to do this... Thanks!

I'm just starting out, so tell me if I am not saying this right. As I understand it (based on other posts), you can't depend upon the initial value of a flip flop. I have a set of jk flipflops with set/reset pins (CD4027B) and I wanted to know if the power-on-reset logic that I made makes sense.

1) is it true that you can't depend upon the initial value of a flip flop, or is this chip or technology (cmos vs ttl) dependent?

2) here is a falstad link to my por design (sort of, it is a bit simplified because the jk in falstad doesn't have set/reset pins and my actual project uses multiple jks chained together and fed from a 555). The wire hanging after the capacitor is meant to feed the reset pin.

The thing that has me sketched out is the connection from the transistor emitter back to it's base. It seems to work in falstad, but I'm wondering if anyone knows if this is insane and if there is an easier way to do this... Thanks!