Junus2012

Advanced Member level 5

Hello,

I am using the Assura package with the Cadence Virtuoso,

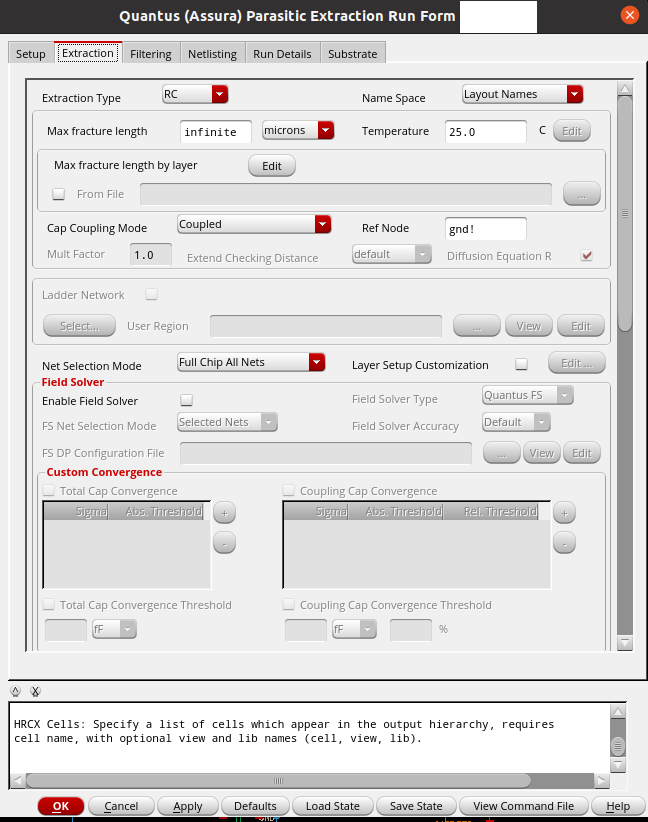

When I do the layout extraction from Quantos, I see that it will be performed at specific temperature, by default is at room temperature (25 °C) as you can see from the image below.

However, I want to do the post-layout simulation by sweeping the temperature from -40 to 85 °C with step size of 0.5 °C. What I am thinking ia that the post-layout simulation, in this case, will only be valid at the temperature where it is extracted, on the other hand it is not realistic or practical to sweep the extraction for the tested range.

Please I need you explanation for this issue.

Thank you in advance

Regards

I am using the Assura package with the Cadence Virtuoso,

When I do the layout extraction from Quantos, I see that it will be performed at specific temperature, by default is at room temperature (25 °C) as you can see from the image below.

However, I want to do the post-layout simulation by sweeping the temperature from -40 to 85 °C with step size of 0.5 °C. What I am thinking ia that the post-layout simulation, in this case, will only be valid at the temperature where it is extracted, on the other hand it is not realistic or practical to sweep the extraction for the tested range.

Please I need you explanation for this issue.

Thank you in advance

Regards