sharankumargoud

Newbie level 6

HI all

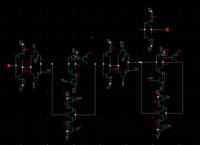

Can u guys please help me about the working and schematic of the pos edge async dff with active low set.

I am bit confused . Thanks in advanced

Can u guys please help me about the working and schematic of the pos edge async dff with active low set.

I am bit confused . Thanks in advanced