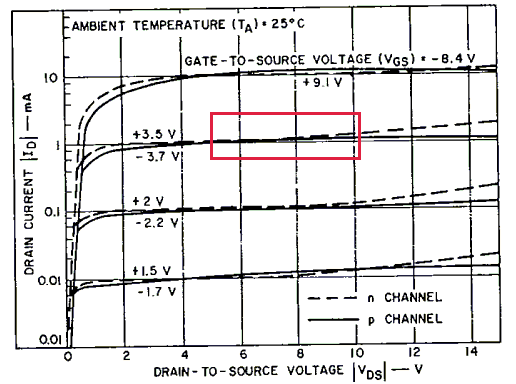

OK, just to clarify the question of what I was trying to measure, here's the relevant graph, taken from a very old "CA3600E" (later renamed CD4007) data sheet.

It's the data in the red rectangle that I was interested in (Id = 1 mA, Vds = 5 to 10 V):

Now according to these curves, the output resistance of the PMOS device should actually be higher than that of the NMOS device (as the solid line shows the PMOS characteristics and it is visibly closer to a constant current source behaviour than the NMOS). So based on this data my measurement results make even less sense, unless, of course

(a) the CMOS technology has changed and these curves are no longer valid for newer variants of the chip, or

(b) the published data was incorrect and they mixed up the NMOS and PMOS curves.

However, that's the only data I was able to find. To be fair, I am somewhat suspicious of its validity because it suggests that Vgs corresponding to 1 mA drain current should be about 3.5 ... 3.7 V but I measured way lower than that, for the various devices I have it was about 2.7V ... 2.9V. Also, I measured higher transconductance values too (about 50% more than the data sheet suggests).

By the way, this prompts a further question to those of you who are familiar with the semiconductor manufacturing. Clearly there are some very old legacy devices that were designed in times when the technology was very different. Such as the CD4000 series. Now, 50 years after they were introduced, they are still being manufactured. Is it done still using the same old process? Or has the silicon actually changed and what I'm buying now is just a functional equivalent but actually made with an updated process?