preethi19

Full Member level 5

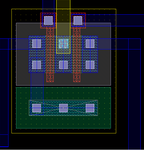

Hi i am doing layout and i read many posts saying we get soft connection error if the bulk of pmos is not given to vdd. But i need to connect the bulk to drain and this connection goes to the drain of another transistor. I am getting the "soft connection error" I couldn't make out much with what others have posted. From what i read i just understood that soft connections error occurs when connections are given through non routing layer (active and n-well). First of all can anyone please explain why does this cause a problem. Why should bulk to always to vdd and if to others an error occurs. And also can anyone please give let me know how to correct this error. Thank you!!!

Attachments

Last edited: