sushl

Junior Member level 2

Hello All i'm looking to implement a PLL with the following specification through rtl code.

Requirement:

Develop an RTL PLL (phase-locked loop) logic with holdover functionality to ensure continuous phase synchronization of the output signal (pll_out) to the reference signal (signal_1) even during temporary unavailability of signal_1.

Functional Specifications:

Requirement:

Develop an RTL PLL (phase-locked loop) logic with holdover functionality to ensure continuous phase synchronization of the output signal (pll_out) to the reference signal (signal_1) even during temporary unavailability of signal_1.

Functional Specifications:

- Input Signals:

- signal_1: 8KHz Phase-synced Reference Clock

- signal_2: 8KHz Local Clock

- clk_ref: 25MHz Clock

- Output Signal:

- pll_out: Output of PLL locked to signal_1

- Normal Operation:

- When signal_1 is present, pll_out should be phase-locked to signal_1.

- Holdover Operation:

- When signal_1 becomes unavailable, the pll_out should enter holdover mode.

- In holdover mode, pll_out should maintain the last known phase of signal_1.

- pll_out should use signal_2 as the 8KHz reference clock to maintain phase synchronization.

- Recovery from Holdover:

- When signal_1 becomes available again, pll_out should smoothly transition out of holdover mode and regain phase synchronization with signal_1.

- Performance:

- The PLL should achieve rapid phase synchronization with the input signals.

- The PLL should maintain low phase and frequency jitter in both normal and holdover modes.

- Resource Utilization:

- The PLL should minimize resource utilization on the FPGA or ASIC.

- Robustness:

- The PLL should be tolerant to occasional glitches or noise on the input signals.

- Testability:

- The PLL should include design features for easy testing and verification.

Since PLL's inside my FPGA typically operate at MHz input range i cannot use inbuilt PLL primitives or ip. My device is a cycloneiv fpga.

- The PLL should include design features for easy testing and verification.

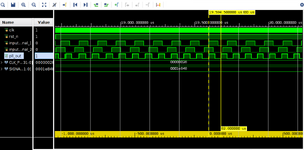

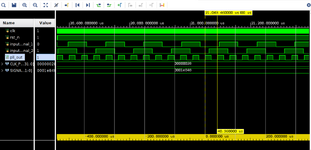

![vivado_6_103Khz_counter[11].PNG](/data/attachments/116/116777-b94374273f2774bc9295793b5d4cb705.jpg)