Fever

Junior Member level 1

Hi,

I'm trying to layout a SMPS that gets 12V, ad outputs 3.3V. The maximal current will not exceed 1 Amp.

I would like to know what you think about this layout, and if there is major or minor issues.

More importantly, I am a bit confused about a line in the datasheet saying "5. Do not allow switching current to flow under the device."

I guess that's exactly what I'm doing and would like to know why it is so important.

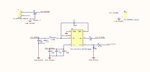

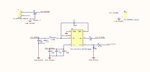

Schematic

Top layer

Bottom layer

3D view

Note : Please ignore badly placed designators, they were placed in a hurry.

Thank you very much.

I'm trying to layout a SMPS that gets 12V, ad outputs 3.3V. The maximal current will not exceed 1 Amp.

I would like to know what you think about this layout, and if there is major or minor issues.

More importantly, I am a bit confused about a line in the datasheet saying "5. Do not allow switching current to flow under the device."

I guess that's exactly what I'm doing and would like to know why it is so important.

Schematic

Top layer

Bottom layer

3D view

Note : Please ignore badly placed designators, they were placed in a hurry.

Thank you very much.