stevenv07

Member level 2

Hello everyone,

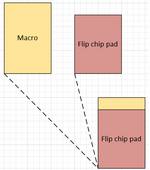

In my design, I have an analog hard macro and its flip-chip pads. Their GDS and LEF files are separate.

I implemented a block design with this macro, its flip-chip pads, and its controller in Cadence Innovus.

Can I place this flip-chip pad over the hard macro in Innovus (see the attached figure)? If yes, could you show me how to place them and the command to do it?

Thanks so much.

Steve.

In my design, I have an analog hard macro and its flip-chip pads. Their GDS and LEF files are separate.

I implemented a block design with this macro, its flip-chip pads, and its controller in Cadence Innovus.

Can I place this flip-chip pad over the hard macro in Innovus (see the attached figure)? If yes, could you show me how to place them and the command to do it?

Thanks so much.

Steve.