ZionWi1

Newbie

Hello all,

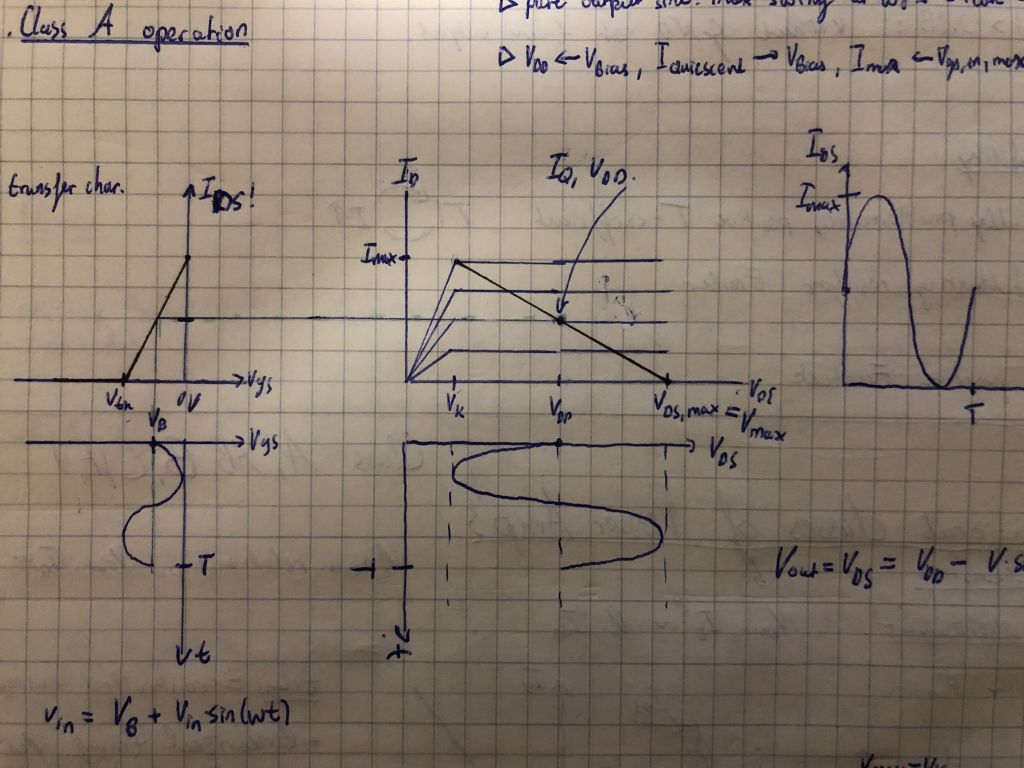

I have been studying Class A and Class B power amp., and according to my lecture script R_opt_load_classA&B = (V_max-V_knee)/I_max applies. I can see this in the output characteristic of the transistor:

Furthermore it is said that the optimal load for Class AB is different: "at Class AB, the Optimum loadline is smaller than R_opt,classA= R_opt,classB". However no formula for an optimal loadline is given. Does a formula for R_opt,classAB depending on the quiescent Current / the conduction angle exist? Or does it need to be determined in a simulation with varying Load resistance?

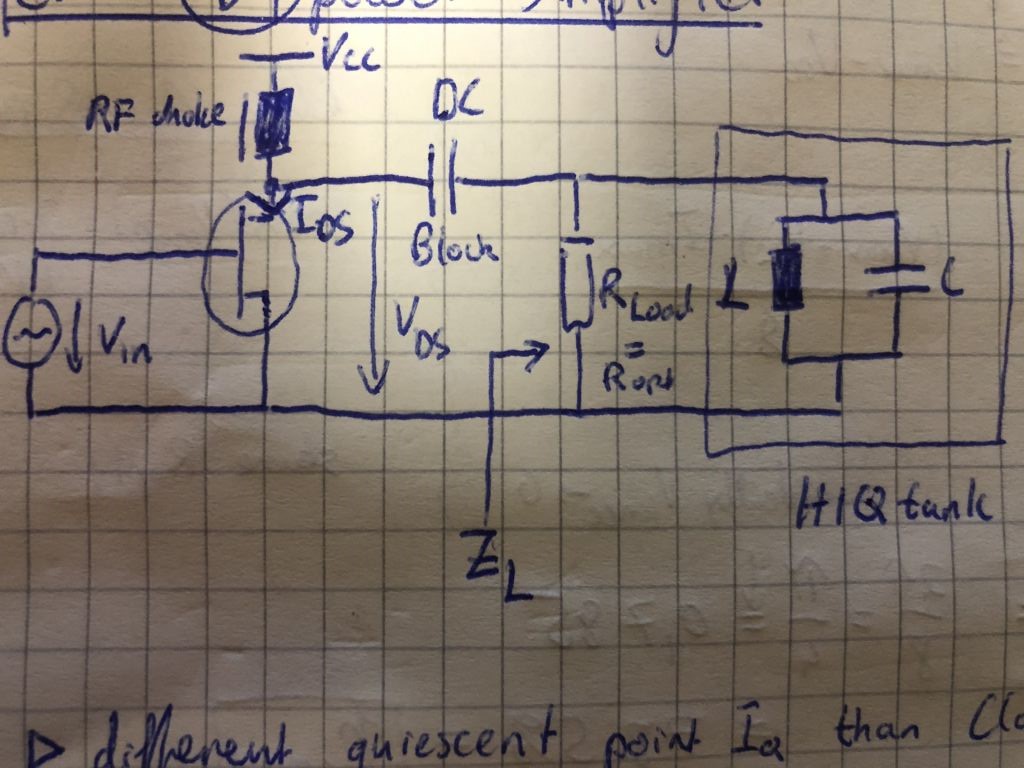

The circuit of the Power Amp in Class AB operation:

I have been studying Class A and Class B power amp., and according to my lecture script R_opt_load_classA&B = (V_max-V_knee)/I_max applies. I can see this in the output characteristic of the transistor:

Furthermore it is said that the optimal load for Class AB is different: "at Class AB, the Optimum loadline is smaller than R_opt,classA= R_opt,classB". However no formula for an optimal loadline is given. Does a formula for R_opt,classAB depending on the quiescent Current / the conduction angle exist? Or does it need to be determined in a simulation with varying Load resistance?

The circuit of the Power Amp in Class AB operation: