navbp

Junior Member level 1

Hi,

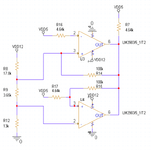

I need help with a circuit using two comparators (LM2903YPT) to identify overvoltage and undervoltage conditions on 12V supply.

If the supply voltage is within a certain range, the output shall be pulled up to 5V.

But if the supply voltage is out of the specified range, the output shall be pulled low by the open collector comparators LM2903.

The circuit diagram is attached.

The simulation works fine. As per simulation,

The undervoltage threshold trigger is 10.35V and 11.2V (due to hysteresis).

The overvoltage threshold trigger is 13.285V and 13.45V (due to hysteresis).

Between 11.2V to 13.2V, the LM2903 output is high according to simulation.

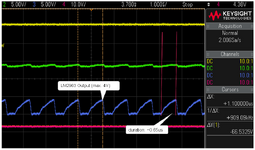

But in reality, noise is observed at the output of LM2903.

The problem is when the supply voltage is near the undervoltage or overvoltage thresholds.

When the VDD12 supply is within the correct range, then the circuit works as expected.

When the VDD12 supply is very low or very high away from the threshold, then the circuit works as expected.

But noise of ~900kHz is observed at the output of the LM2903. The hysteresis is considered but even then, the noise is observed when VDD12 is near these threshold values.

The screenshot of the observed noise is attached.

Please help me to understand what is the reason for this noise and how to correct the circuit.

Thank you.

I need help with a circuit using two comparators (LM2903YPT) to identify overvoltage and undervoltage conditions on 12V supply.

If the supply voltage is within a certain range, the output shall be pulled up to 5V.

But if the supply voltage is out of the specified range, the output shall be pulled low by the open collector comparators LM2903.

The circuit diagram is attached.

The simulation works fine. As per simulation,

The undervoltage threshold trigger is 10.35V and 11.2V (due to hysteresis).

The overvoltage threshold trigger is 13.285V and 13.45V (due to hysteresis).

Between 11.2V to 13.2V, the LM2903 output is high according to simulation.

But in reality, noise is observed at the output of LM2903.

The problem is when the supply voltage is near the undervoltage or overvoltage thresholds.

When the VDD12 supply is within the correct range, then the circuit works as expected.

When the VDD12 supply is very low or very high away from the threshold, then the circuit works as expected.

But noise of ~900kHz is observed at the output of the LM2903. The hysteresis is considered but even then, the noise is observed when VDD12 is near these threshold values.

The screenshot of the observed noise is attached.

Please help me to understand what is the reason for this noise and how to correct the circuit.

Thank you.