X

Xenon02

Guest

Hello !

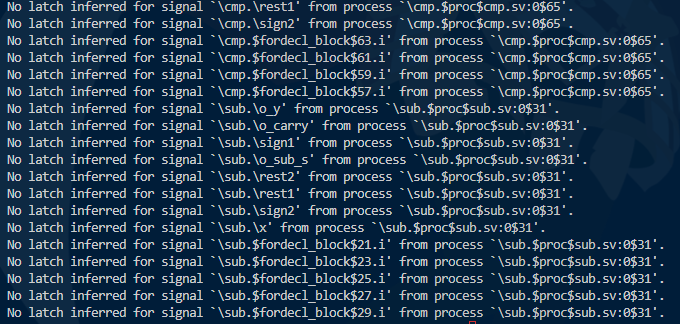

I have a problem because I can't use yosys to sythesize this code. Whenever I try to do it this appears :

I don't know where are the latches in my code

Here is the code :

Can someone help me with this ?

I have a problem because I can't use yosys to sythesize this code. Whenever I try to do it this appears :

I don't know where are the latches in my code

Here is the code :

`include "definictions.vh"

module exe_unit_w31 (i_oper, i_argA, i_argB, i_clk, i_rsn, o_status, o_result);

input logic [`OPER_BITS-1:0] i_oper;

input logic [`BITS-1:0] i_argA, i_argB;

input logic i_clk;

input logic i_rsn;

output logic [3:0] o_status;

output logic [`BITS-1:0] o_result;

logic [`BITS-1:0] s_argA, s_argB;

logic [`BITS-1:0] s_oper;

logic [`BITS-1:0] s_y_sub;

logic [`BITS-1:0] s_y_cmp;

logic [`BITS-1:0] s_y_to0;

logic [`BITS-1:0] s_y_ZM2U2;

logic s_carry_sub;

logic s_err_to0;

logic s_err_ZM2U2;

logic sign3;

sub sub_exe (.i_a(s_argA), .i_b(s_argB), .o_y(s_y_sub), .o_carry(s_carry_sub));

cmp cmp_exe (.i_a(s_argA), .i_b(s_argB), .o_y(s_y_cmp));

to0 to0_exe (.i_a(s_argA), .i_b(s_argB), .o_y(s_y_to0), .o_err(s_err_to0));

ZM2U2 ZM2U2_exe (.i_a(s_argA), .o_y(s_y_ZM2U2), .o_err(s_err_ZM2U2));

integer ones;

integer i;

always_ff @(posedge i_clk)

begin

if(!i_rsn)

begin

s_oper <= '0;

s_argA <= '0;

s_argB <= '0;

end

else

begin

s_oper <= i_oper;

s_argA <= i_argA;

s_argB <= i_argB;

end

end

always_comb

begin

o_status = '0;

o_result = '0;

s_y_cmp = '0;

s_y_sub = '0;

s_y_to0 = '0;

s_y_ZM2U2 = '0;

s_oper = '0;

sign3 = '0;

s_carry_sub ='0;

s_err_to0 ='0;

s_err_ZM2U2 = '0;

case(s_oper)

`SUBTRACT:

begin

o_result = s_y_sub;

o_status[3] = 0;

end

`COMPARE:

begin

o_result = s_y_cmp;

o_status[3] = 0;

end

`CHANGE:

begin

o_result = s_y_to0;

if(s_err_to0)

o_status[3] = 1;

end

`CONVERSION:

begin

o_result = s_y_ZM2U2;

if(s_err_ZM2U2)

o_status[3] = 1;

end

default:

begin

o_result = '0;

o_status = 4'b1000;

end

endcase

for(int i = 0; i<`BITS ;i++)

begin

if(i ==`BITS-1)

begin

sign3 = o_result;

end

end

//NEG

if(i_oper!= 'd0)

begin

if(sign3 == 1)

begin

o_status[2] = 1;

end

end

else

begin

if(s_carry_sub == 1)

o_status[2] = 1;

else

begin

if(sign3 == 1)

begin

o_status[2] = 1;

end

end

end

//EVEN

ones = 0;

for(i = `BITS-1; i>=0; i = i-1)

begin

if(o_result == 1)

ones = ones + 1;

end

if(!(ones % 2))

o_status[1] = 1;

//ONES

if(ones == `BITS)

o_status[0] = 1;

end

endmodule

Can someone help me with this ?