d123

Advanced Member level 5

Hi,

Just messing around, trying to learn a few things about typical circuits which I think are useful building blocks... I will not be going into mass production with this design, I'm just working through ideas for - and the issues for beginners related to - voltmeter sections. Even so, a little experienced input would be gratefully received as I am perplexed as to the cause of this problem.

I am working on this idea, the circuit here in the schematics, anyone with eyes can see that it is not related to a PSoC, an MCU, a breakout board, a development board or any such thing which has nothing to do with this circuit, please and thank you in advance.

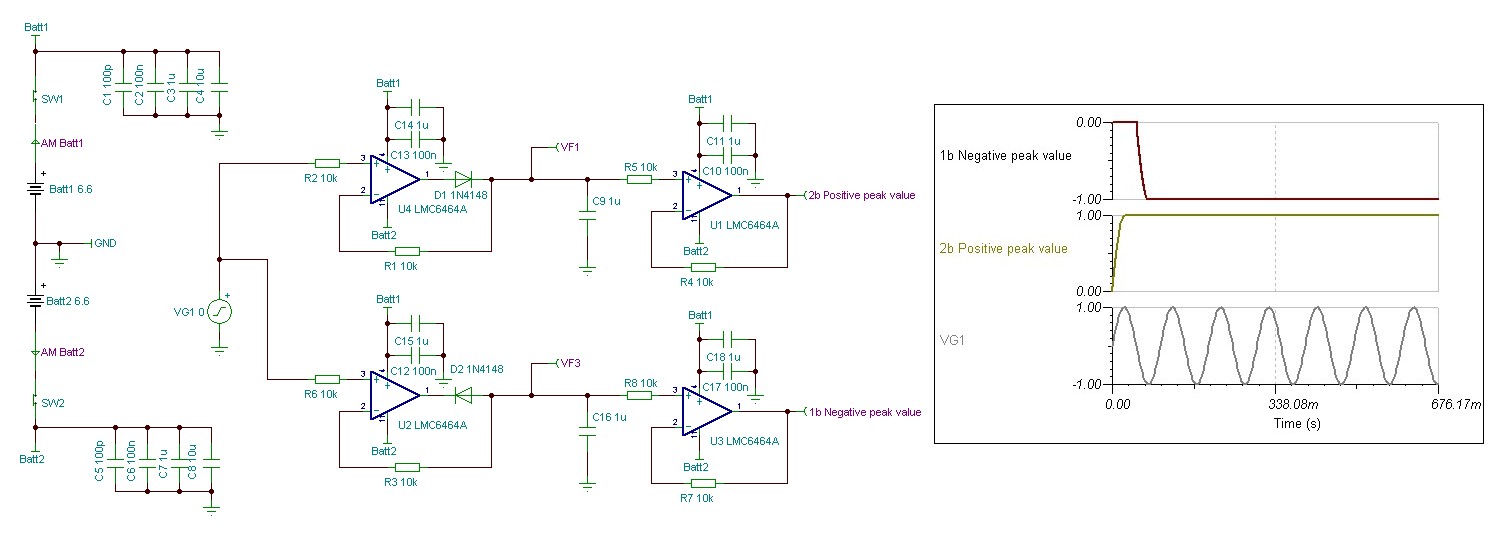

I copied the 'Two-Stage Peak Detector' circuit (page 9, figure 24) from the great Microchip application note attached here and simulated it. It works/simulates (what looks to me) correctly, as can be seen from the schematic and transient results that follow. Positive peak holds at +1V, negative peak holds at -1V.

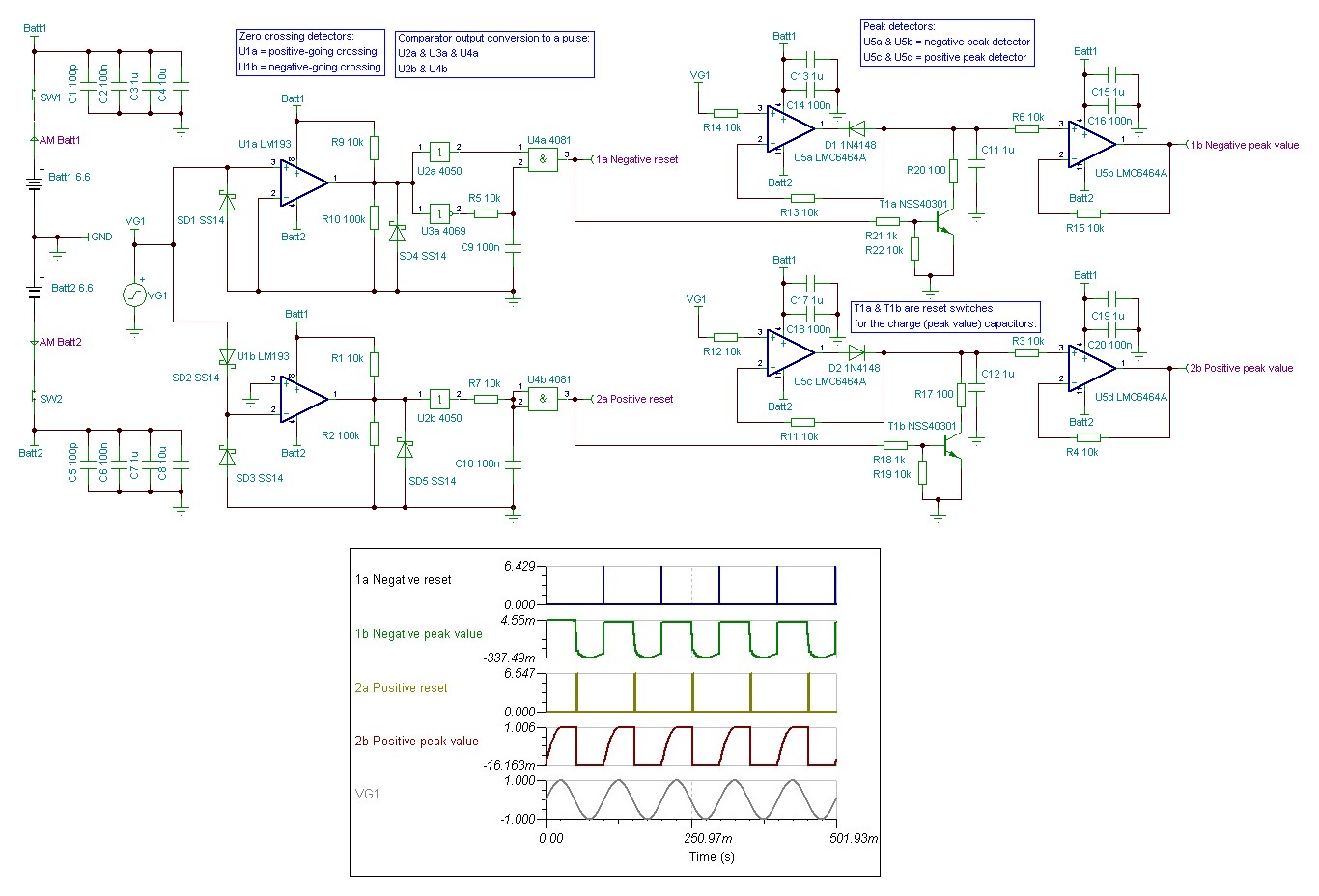

When I connect the peak detector circuit to a zero crossing detector circuit - the ZCD is there so as to discharge the peak value capacitors periodically - the negative peak value is no longer reaching -1V, it only goes to ~340mV, as can be seen from the second schematic and transient results below. It does this connected or not to the T1a reset circuitry.

I've been messing around with this for a while today (removing things such as the negative reset BJT section, buffering the peak detector inputs, feeling stupid and ignorant, etc.) with no success in recovering the -1Vpeak in = -1Vpeak out signal the negative peak detector produces when not connected to the negative reset/ZCD circuit, and by now I can only dimly understand that it is just some 'newbie' error (of reasoning/design) that I am committing for the negative peak to fall from -1V to -340mV or the simulator has some issue with the ZCD circuit being in the same schematic (I wish - blame the tools, not the idiot). Is this something to do with the simulator or it is actually something about the design?

Can anyone help me see what is incorrect about the negative peak detector section and ZCD and reset circuitry to make it do that, please?

Thanks.

Just messing around, trying to learn a few things about typical circuits which I think are useful building blocks... I will not be going into mass production with this design, I'm just working through ideas for - and the issues for beginners related to - voltmeter sections. Even so, a little experienced input would be gratefully received as I am perplexed as to the cause of this problem.

I am working on this idea, the circuit here in the schematics, anyone with eyes can see that it is not related to a PSoC, an MCU, a breakout board, a development board or any such thing which has nothing to do with this circuit, please and thank you in advance.

I copied the 'Two-Stage Peak Detector' circuit (page 9, figure 24) from the great Microchip application note attached here and simulated it. It works/simulates (what looks to me) correctly, as can be seen from the schematic and transient results that follow. Positive peak holds at +1V, negative peak holds at -1V.

When I connect the peak detector circuit to a zero crossing detector circuit - the ZCD is there so as to discharge the peak value capacitors periodically - the negative peak value is no longer reaching -1V, it only goes to ~340mV, as can be seen from the second schematic and transient results below. It does this connected or not to the T1a reset circuitry.

I've been messing around with this for a while today (removing things such as the negative reset BJT section, buffering the peak detector inputs, feeling stupid and ignorant, etc.) with no success in recovering the -1Vpeak in = -1Vpeak out signal the negative peak detector produces when not connected to the negative reset/ZCD circuit, and by now I can only dimly understand that it is just some 'newbie' error (of reasoning/design) that I am committing for the negative peak to fall from -1V to -340mV or the simulator has some issue with the ZCD circuit being in the same schematic (I wish - blame the tools, not the idiot). Is this something to do with the simulator or it is actually something about the design?

Can anyone help me see what is incorrect about the negative peak detector section and ZCD and reset circuitry to make it do that, please?

Thanks.