kalinowskikswonilak

Newbie level 2

It's my first post so hello everybody.

Firstly, I'd like to say that I'm real nwb as far as analog IC design is concerned and I have some really basic questions:

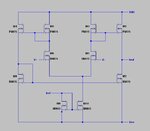

I'd like to calculate parameters(W/L) of transistors to achieve transconductance of the simpliest ota(schematic attached) around 100mS. No other requirements, technology 0.35um.

I've already briefly read Analog design essentials and Allen Holberg book but honestly I have no idea where to start to calculate dimmensions of transistors.

Any help and sample calculations would be greatly appreciated.

ps. I've read several ee240 reports but they're way too complicated for such a simple project as mine.

cheers,

michal

Firstly, I'd like to say that I'm real nwb as far as analog IC design is concerned and I have some really basic questions:

I'd like to calculate parameters(W/L) of transistors to achieve transconductance of the simpliest ota(schematic attached) around 100mS. No other requirements, technology 0.35um.

I've already briefly read Analog design essentials and Allen Holberg book but honestly I have no idea where to start to calculate dimmensions of transistors.

Any help and sample calculations would be greatly appreciated.

ps. I've read several ee240 reports but they're way too complicated for such a simple project as mine.

cheers,

michal