pr0wl3r

Newbie

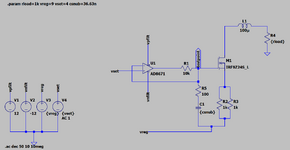

Hi, I have to perform stability analysis on an op-amp (AD8671) which is being used as an op-amp in the circuit attached. I am using LTSpice to perform this. My approach is to give a 1V AC small signal at the input and see the frequency response at the 'testpoint' which should, if I am correct, provide me with the gain and phase of the transfer function. For this, I am trying to adjust the conditions so that I am able to create critical points, with (Gain > 1) and (Phase Shift = 180 degrees). I also need to check the effect of the snubber circuit attached to the node, as theoretically, with improper values of the same, the response should be unstable.

However, as of yet, I am unable to effectively see this, primarily because the gain is always <-160 dB as shown in attached image, in both open loop and closed loop conditions. Also, if I try to perform a transient analysis, the simulation is jittery, often getting stuck after a point and simulating at xyz nanoseconds/sec, which is obnoxiously slow.

My questions are:

1. Is my approach correct?

2. Is my circuit and script implementation, correct?

3. If the answer to either of the above is no, what should I do/change?

4. How do I speed up the transient response? (if possible)

Attached are relevant images of circuit and its frequency response, and the .asc files used by LTSpice. Any help would be appreciated

However, as of yet, I am unable to effectively see this, primarily because the gain is always <-160 dB as shown in attached image, in both open loop and closed loop conditions. Also, if I try to perform a transient analysis, the simulation is jittery, often getting stuck after a point and simulating at xyz nanoseconds/sec, which is obnoxiously slow.

My questions are:

1. Is my approach correct?

2. Is my circuit and script implementation, correct?

3. If the answer to either of the above is no, what should I do/change?

4. How do I speed up the transient response? (if possible)

Attached are relevant images of circuit and its frequency response, and the .asc files used by LTSpice. Any help would be appreciated