cookies1427

Newbie

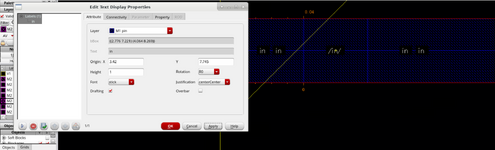

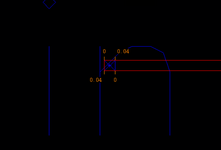

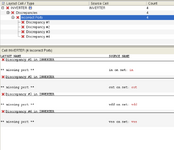

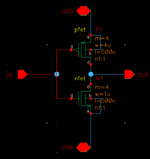

Can anybody help out a beginner here? I keep having this discrepancy error in my lvs report talking about these missing ports. Upon looking at different forums, it always says that I have to use a specific type of metal layer. So, I made sure that the nets have M1 pin layer similar with its label. Since it is also said that it is case sensitive, I made sure to name them properly.

After all these, these errors keep showing. I have attached the necessary screenshot in my layout.

Any answer is highly appreciated. Thanks boss!

After all these, these errors keep showing. I have attached the necessary screenshot in my layout.

Any answer is highly appreciated. Thanks boss!