ardique

Junior Member level 2

Hi all,

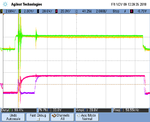

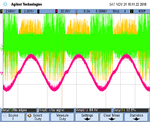

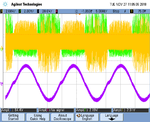

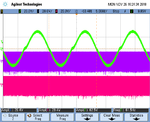

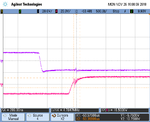

I'm currently work on a 1kVA full-bridge single phase inverter with SPWM current control. However, during my testing on open loop with lower rating test (60Vdc, Rload = 11.6ohm, Irated = 3A), I have problem at my high side switching pair (Q3). Attached are the schematic, pcb layout design and the waveform that I measure on Vgs on Q2(pink color) and Q3(purple color). Since the problem is occurred at pair of Q2&Q3 that I'm working with. Please let me know what did I missed or wrongly do the connection.

I'm using CoolMOS power transistor (SPW35N60C3), MINMAX(MCW03-24D15), gate driver (TLP350).

Moreover, the spwm signal generated from DSP also affected by the distortion as shown in waveform.

Your cooperation is very much appreciated.

Thank you.

I'm currently work on a 1kVA full-bridge single phase inverter with SPWM current control. However, during my testing on open loop with lower rating test (60Vdc, Rload = 11.6ohm, Irated = 3A), I have problem at my high side switching pair (Q3). Attached are the schematic, pcb layout design and the waveform that I measure on Vgs on Q2(pink color) and Q3(purple color). Since the problem is occurred at pair of Q2&Q3 that I'm working with. Please let me know what did I missed or wrongly do the connection.

I'm using CoolMOS power transistor (SPW35N60C3), MINMAX(MCW03-24D15), gate driver (TLP350).

Moreover, the spwm signal generated from DSP also affected by the distortion as shown in waveform.

Your cooperation is very much appreciated.

Thank you.