jonnybgood

Full Member level 4

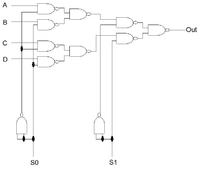

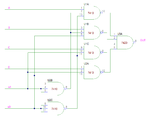

I've constructed a 4-1 multiplexor with and not and or gates, then i converted it to nand gates. I removed the extra not gates to simplify and was left with the circuit attached. Do you guys think it is simplified enough?

thanks

Brandon

thanks

Brandon