engr_joni_ee

Advanced Member level 3

Hello,

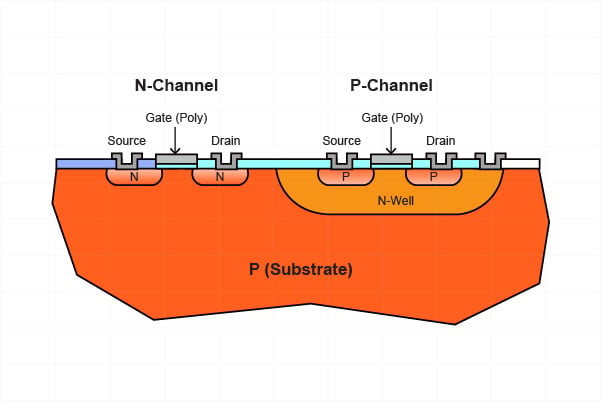

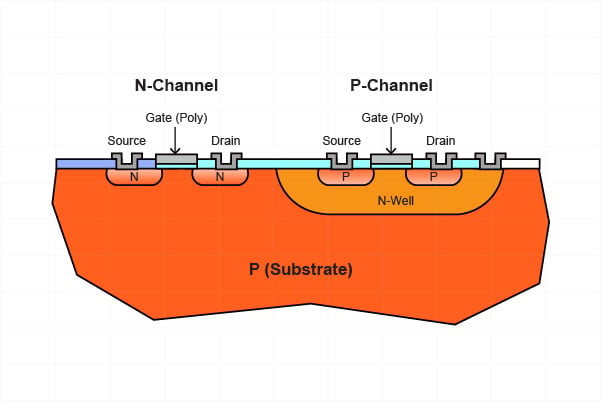

In MOFET devices, the channel is established between Drain and Source when a certain voltage is applied at the Gate, is that true ?

The channel is made of P-Type material in PMOS and the channel is made of N-Type material in NMOS, right ?

In the following link, the symbols in Figure 1 are wrong ?

The symbols in Figure 4 and Figure 6 are ok. Please confirm. Thanks in advance.

www.allaboutcircuits.com

www.allaboutcircuits.com

In MOFET devices, the channel is established between Drain and Source when a certain voltage is applied at the Gate, is that true ?

The channel is made of P-Type material in PMOS and the channel is made of N-Type material in NMOS, right ?

--- Updated ---

In the following link, the symbols in Figure 1 are wrong ?

The symbols in Figure 4 and Figure 6 are ok. Please confirm. Thanks in advance.

MOSFET Structure and Operation for Analog IC Design - Technical Articles

Learn about the theory and implementation of MOSFETs, a key component of today’s analog integrated circuits.