mohamis288

Full Member level 3

Hello,

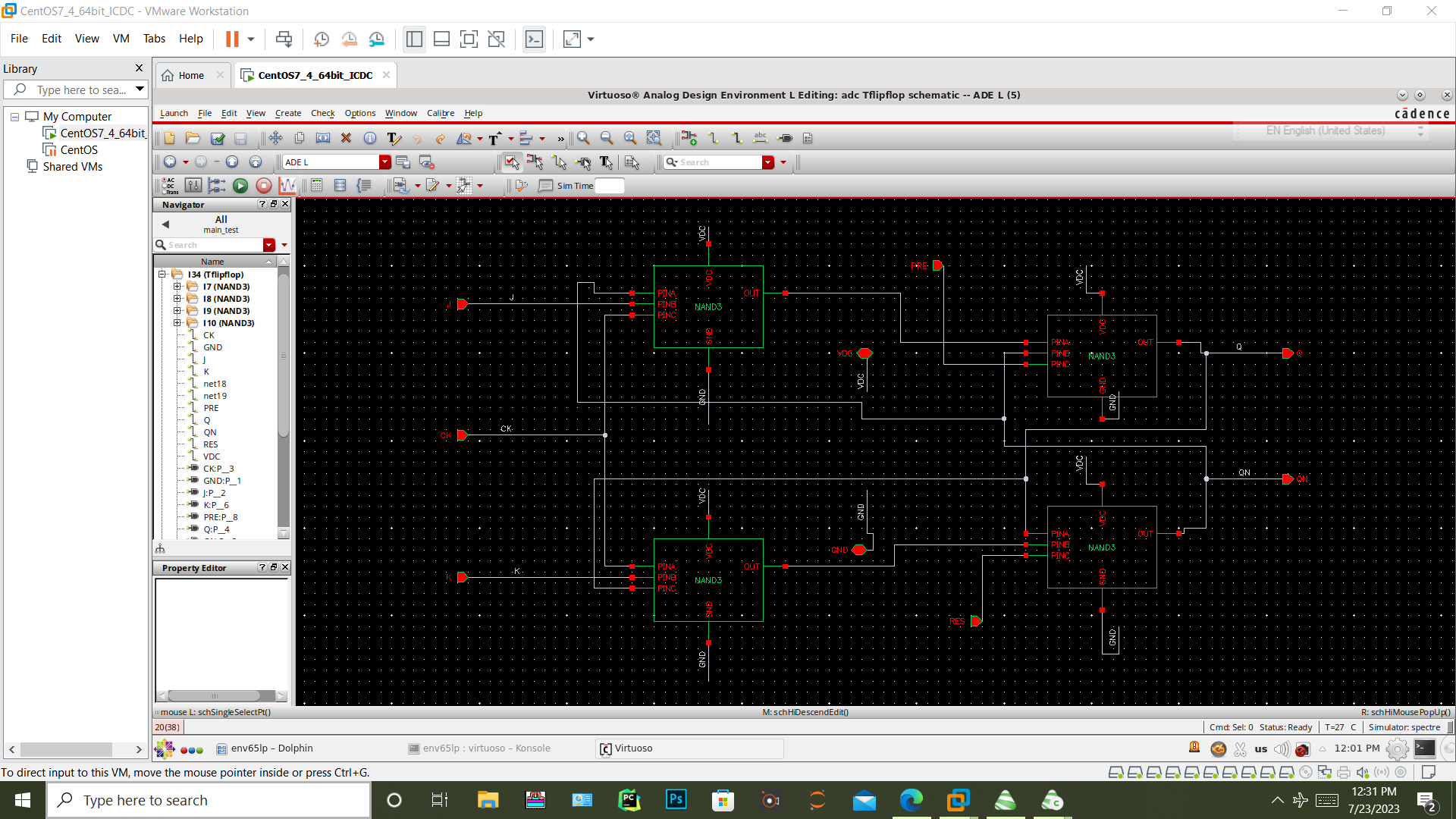

I have created a flip-flop using the following structure:

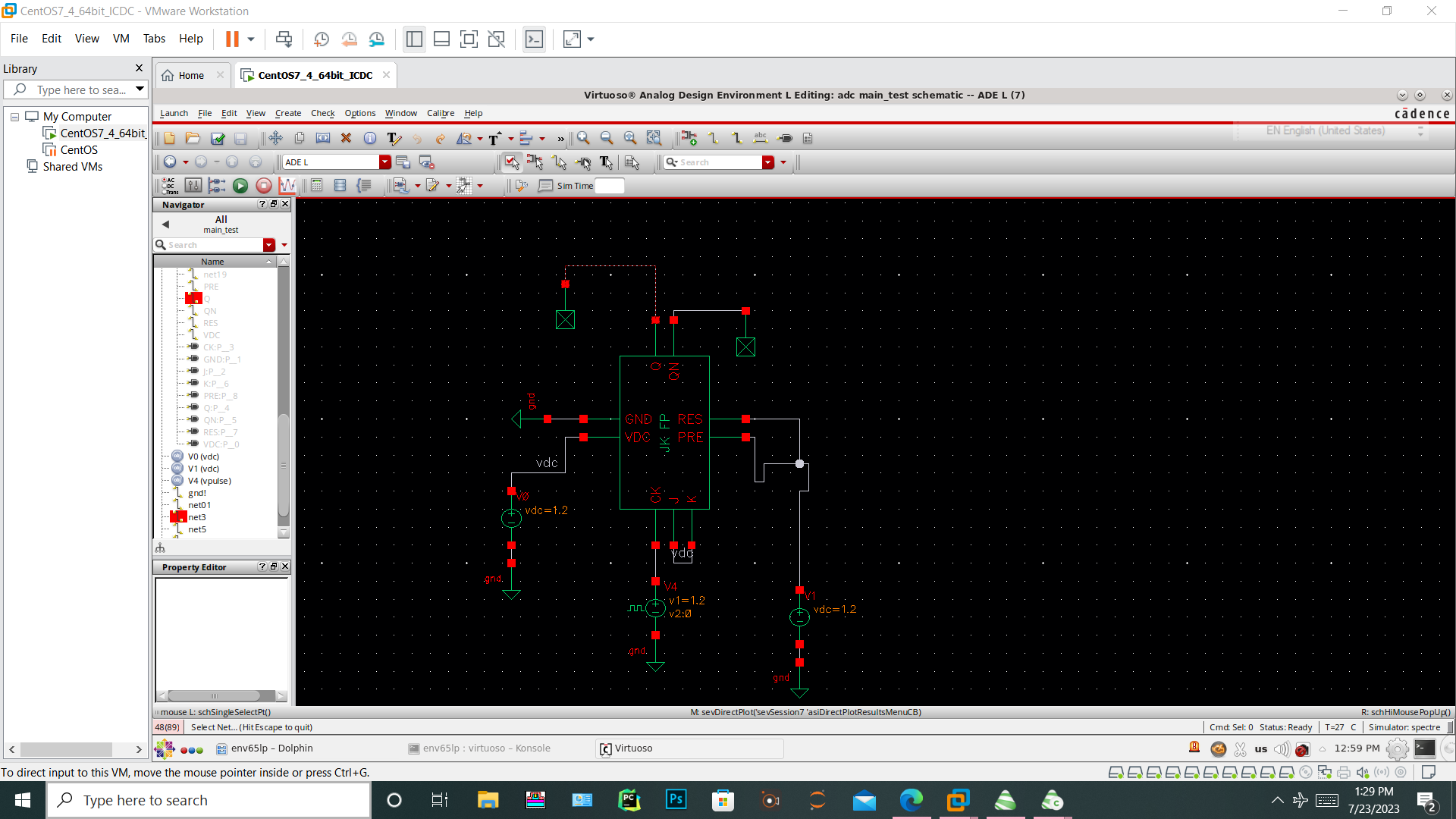

it is my flip-flop testbench circuit:

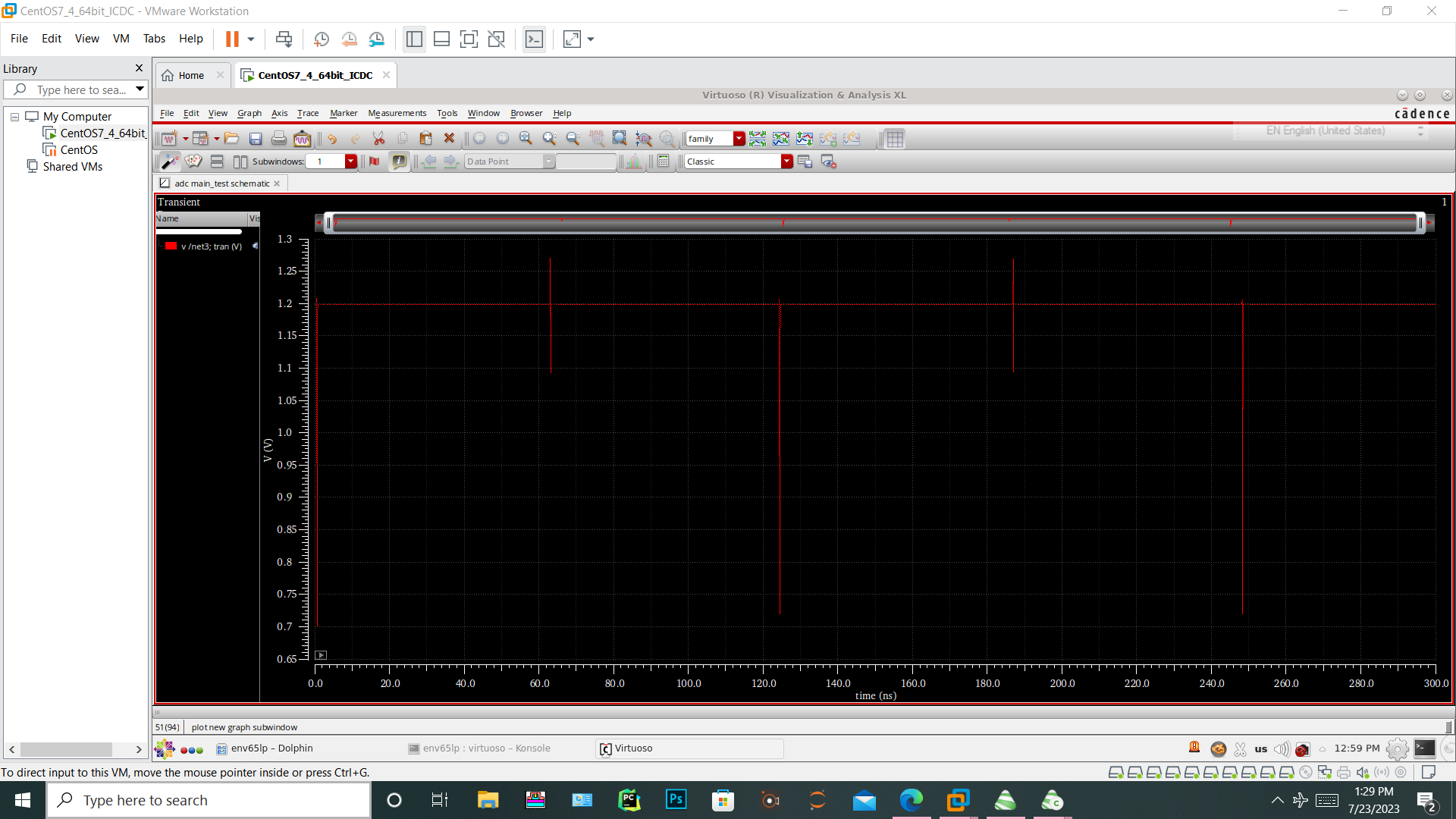

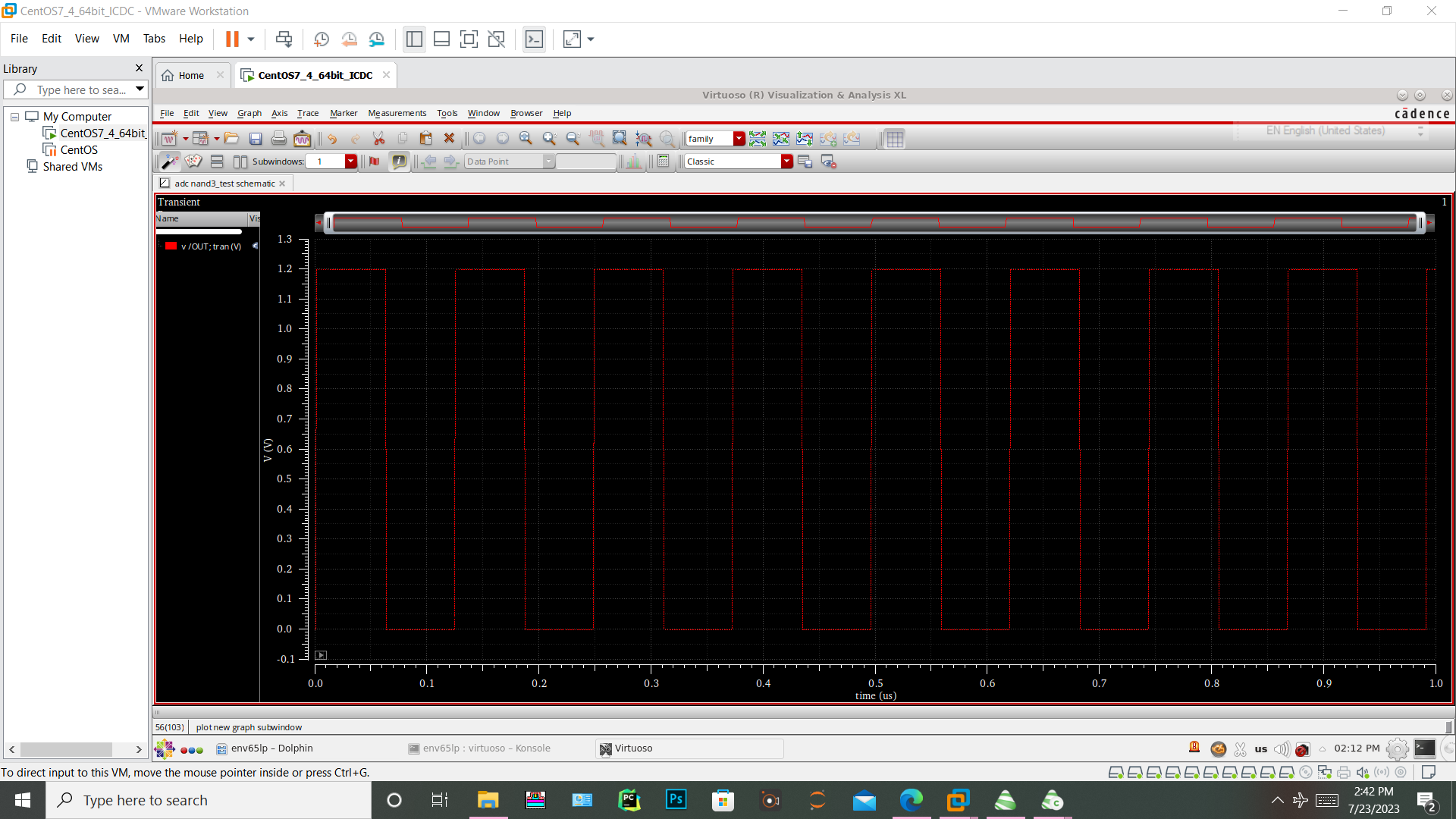

I have simulated this circuit and here is output result:

it seems it wants to change, but it can not. what is the problem do you think?

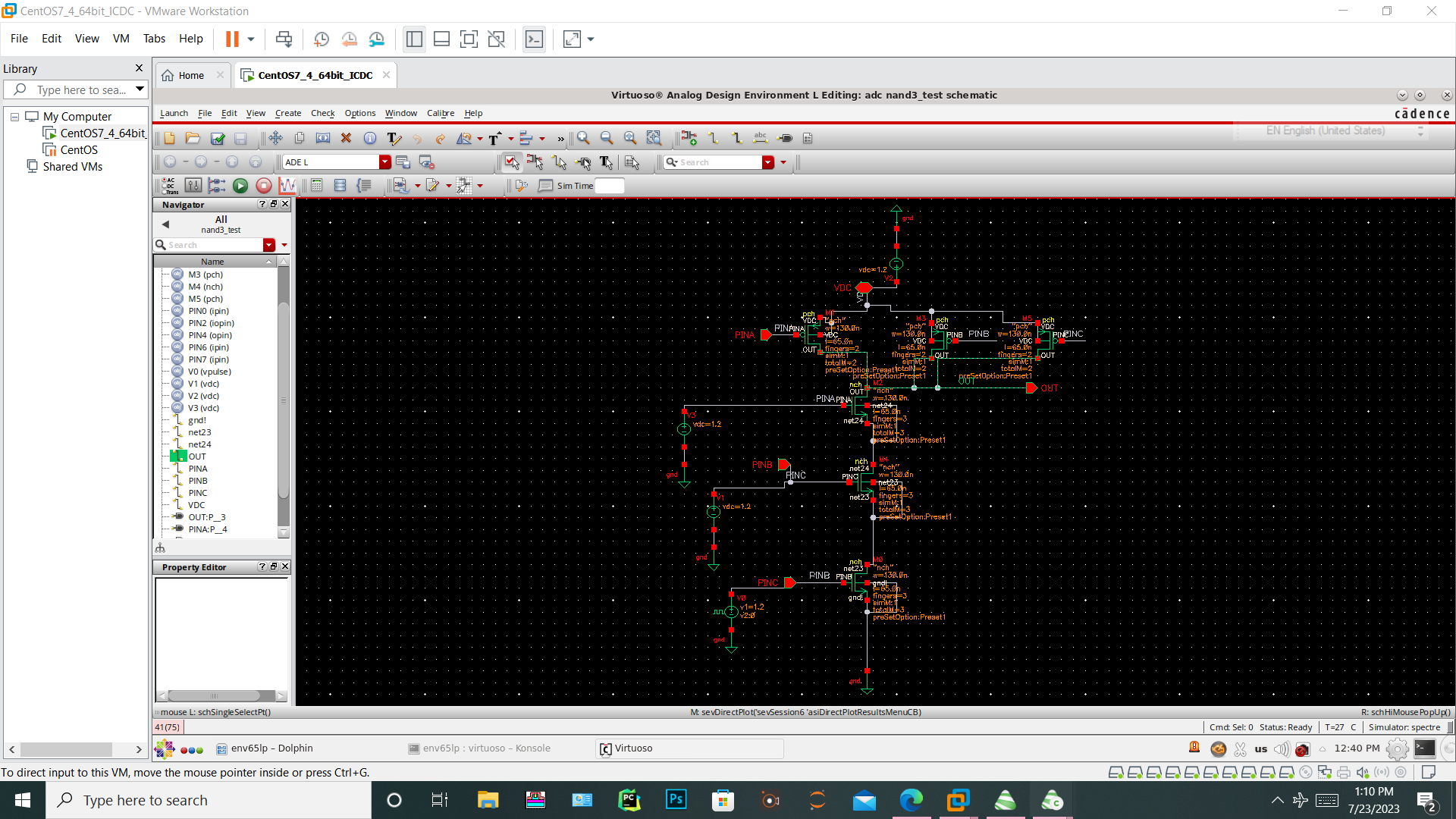

I have tested Nand3 lonely in schematic and it works correctly. here is the testbench for simulation of NAND3 and output result of NAND3:

I have created a flip-flop using the following structure:

it is my flip-flop testbench circuit:

I have simulated this circuit and here is output result:

it seems it wants to change, but it can not. what is the problem do you think?

I have tested Nand3 lonely in schematic and it works correctly. here is the testbench for simulation of NAND3 and output result of NAND3: