arifboy

Newbie

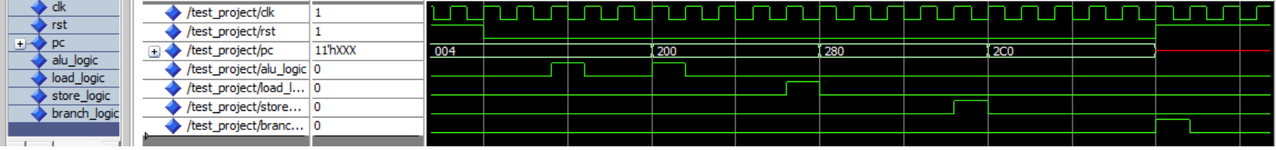

I am working on a VHDL code to insert multiple varying delays to signals. I have shown code below and expected waveforms and present waveforms respectively too. How can the code be changed to get desired waveforms?

Code:

int := conv_integer(pc);

wait until rising_edge(clk);

if (int >= 0 and int <= 500) then -- alu/j

load_logic <= '0';

store_logic <= '0';

branch_logic <= '0';

wait for 20 ns; alu_logic <= '1';

wait for 20 ns; alu_logic <= '0';

elsif (int >= 504 and int <= 600) then --load

alu_logic <= '0';

store_logic <= '0';

branch_logic <= '0';

wait for 40 ns; load_logic <= '1';

wait for 20 ns; load_logic <= '0';

elsif (int >= 604 and int <= 700) then -- store

alu_logic <= '0';

load_logic <= '0';

branch_logic <= '0';

wait for 60 ns; store_logic <= '1';

wait for 20 ns; store_logic <= '0';

else --- br/j

alu_logic <= '0';

load_logic <= '0';

store_logic <= '0';

wait for 80 ns; branch_logic <= '1';

wait for 20 ns; branch_logic <= '0';

end if;

Code:

int := conv_integer(pc);

wait until rising_edge(clk);

if (int >= 0 and int <= 500) then -- alu/j

load_logic <= '0';

store_logic <= '0';

branch_logic <= '0';

wait for 20 ns; alu_logic <= '1';

wait for 20 ns; alu_logic <= '0';

elsif (int >= 504 and int <= 600) then --load

alu_logic <= '0';

store_logic <= '0';

branch_logic <= '0';

wait for 40 ns; load_logic <= '1';

wait for 20 ns; load_logic <= '0';

elsif (int >= 604 and int <= 700) then -- store

alu_logic <= '0';

load_logic <= '0';

branch_logic <= '0';

wait for 60 ns; store_logic <= '1';

wait for 20 ns; store_logic <= '0';

else --- br/j

alu_logic <= '0';

load_logic <= '0';

store_logic <= '0';

wait for 80 ns; branch_logic <= '1';

wait for 20 ns; branch_logic <= '0';

end if;