fredhdx573

Newbie

Hello everyone,

I have a question that I would like to share with you:

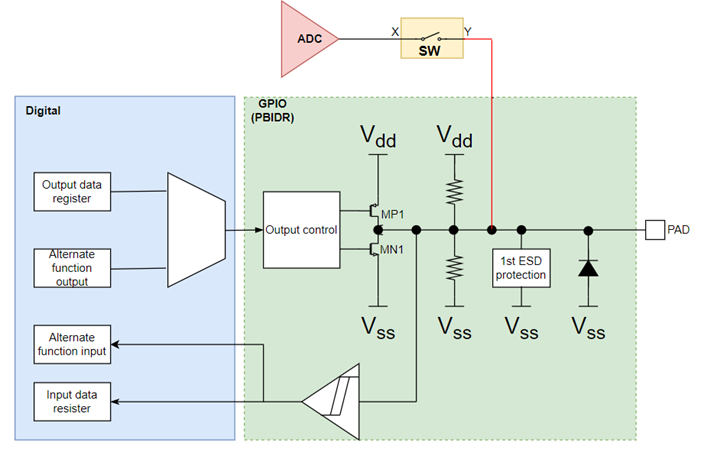

I am currently working on a project where I want to share the input PAD of an ADC with the GPIO's PAD. The main purpose behind this is to save costs. The GPIO PAD supports 5V tolerance, while the ADC only allows a maximum input voltage of 3.6V. I have implemented a switch (transmission gate) between the ADC and the PAD, which allows me to turn off the ADC when it is not in use. However, I have a concern regarding the situation where the PAD voltage is 5V, as it could potentially conduct through the PMOS of the switch and damage the ADC. Could someone please guide me on how to address this issue?

Thank you all for your assistance.

Best regards,

I have a question that I would like to share with you:

I am currently working on a project where I want to share the input PAD of an ADC with the GPIO's PAD. The main purpose behind this is to save costs. The GPIO PAD supports 5V tolerance, while the ADC only allows a maximum input voltage of 3.6V. I have implemented a switch (transmission gate) between the ADC and the PAD, which allows me to turn off the ADC when it is not in use. However, I have a concern regarding the situation where the PAD voltage is 5V, as it could potentially conduct through the PMOS of the switch and damage the ADC. Could someone please guide me on how to address this issue?

Thank you all for your assistance.

Best regards,