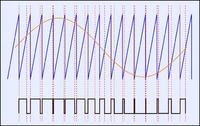

mnfsoft, the second link you provides comes in very handy and is a visual representation of what barry was trying to tell. I have a pretty good idea of what my output from the board needs to look like but im still not fully sure on how to code it to get this:

For a 36-element table between 0-360 degrees I calculated these numbers:

0, 43, 86, 125, 161, 192, 217, 235, 246, 250, 246, 235, 217, 192, 161, 125, 86, 43, 0, -43, -86, -125, -161, -192, -217, -235, -246, -250, -246, -235, -217, -192, -161, -125, -86, -43

How can I put these into xilinx verilog code using the "case" compare way?

Knowing that my clock default input is 50 MHz what should I do with my clock divider?

Thanks for the input!