tumkayaonur

Junior Member level 2

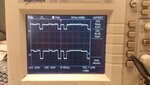

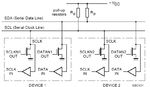

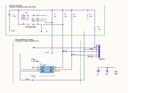

I wrote a verilog code for I2C and tested it. It works properly in simulation results but i can't get any data from slave device's register.

Can anyone help me ?

Can anyone help me ?

Code Verilog - [expand]