BelgianWaffle

Newbie

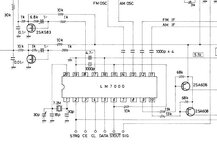

I've always relied on a datasheet to have starting point Icp for loop filter calculation, but I am about to start designing with a LM7001 PLL where there is no CP spec whatsoever.

How would you evaluate the charge pump current? Reason is that I would like to use a passivle lead/lag 3rd order if I can, for noise reasons.

I was thinking of intentionally inputting an incorrect Fin and then measuring voltage drop of the pulses over a series load resistor connected on PDout (there are 2, I'm using the FM one).

I can't see a problem with this but I might be overlooking something.

TIA 73

How would you evaluate the charge pump current? Reason is that I would like to use a passivle lead/lag 3rd order if I can, for noise reasons.

I was thinking of intentionally inputting an incorrect Fin and then measuring voltage drop of the pulses over a series load resistor connected on PDout (there are 2, I'm using the FM one).

I can't see a problem with this but I might be overlooking something.

TIA 73